# WEB-CUSTOMIZABLE, ANY-FREQUENCY, ANY-OUTPUT QUAD CLOCK GENERATOR/BUFFER

#### **Features**

- Low power MultiSynth™ technology enables independent, any-frequency synthesis of four frequencies

- Configurable as a clock generator or clock buffer device

- Three independent, user-assignable, pinselectable device configurations

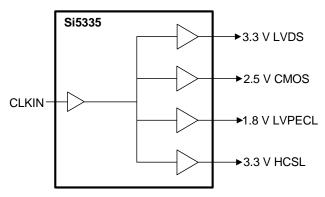

- Highly-configurable output drivers with up to four differential outputs, eight single-ended clock outputs, or a combination of both

- Low phase jitter of 0.7 ps RMS

- Flexible input reference:

- External crystal: 25 or 27 MHz

- CMOS input: 10 to 200 MHz

- SSTL/HSTL input: 10 to 350 MHz

- Differential input: 10 to 350 MHz

- Independently configurable outputs support any frequency or format:

- LVPECL/LVDS/CML: 1 to 350 MHz

- HCSL: 1 to 250 MHz

- CMOS: 1 to 200 MHz

- SSTL/HSTL: 1 to 350 MHz

- Independent output voltage per driver:

1.5, 1.8, 2.5, or 3.3 V

- Single supply core with excellent PSRR: 1.8, 2.5, 3.3 V

- Up to five user-assignable pin functions simplify system design: SSENB (spread spectrum control), RESET, Master OEB or OEB per pin, and Frequency plan select (FS1, FS0)

- Loss of signal alarm

- PCIe Gen 1/2/3/4 common clock compliant

- PCIe Gen 3 SRNS Compliant

- Two selectable loop bandwidth settings: 1.6 MHz or 475 kHz

- Easy to customize with web-based utility

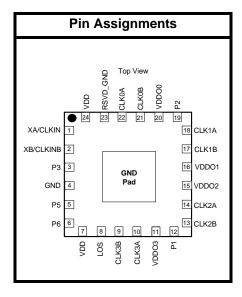

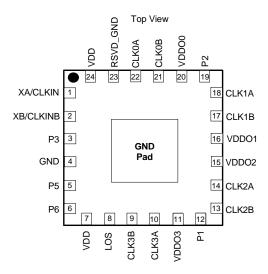

- Small size: 4 x 4 mm, 24-QFN

- Low power (core):

- 45 mA (PLL mode)

- 12 mA (Buffer mode)

- Wide temperature range: –40 to +85 °C

#### **Applications**

- Ethernet switch/router

- PCI Express Gen 1/2/3/4

- PCle jitter attenuation

- DSL jitter attenuation

- Broadcast video/audio timing

- Processor and FPGA clocking

- MSAN/DSLAM/PON

- Fibre Channel, SAN

- Telecom line cards

- 1 GbE and 10 GbE

## **Description**

The Si5335 is a highly flexible clock generator capable of synthesizing four completely non-integer-related frequencies up to 350 MHz. The device has four banks of outputs with each bank supporting one differential pair or two single-ended outputs. Using Silicon Laboratories' patented MultiSynth fractional divider technology, all outputs are guaranteed to have 0 ppm frequency synthesis error regardless of configuration, enabling the replacement of multiple clock ICs and crystal oscillators with a single device. The Si5335 supports up to three independent, pin-selectable device configurations, enabling one device to replace three separate clock generators or buffer ICs. To ease system design, up to five user-assignable and pin-selectable control pins are provided, supporting PCIe-compliant spread spectrum control, master and/or individual output enables, frequency plan selection, and device reset. Two selectable PLL loop bandwidths support jitter attenuation in applications, such as PCle and DSL. Through its flexible ClockBuilder™ (www.silabs.com/ClockBuilder) web configuration utility, factory-customized, pin-controlled devices are available in two weeks without minimum order quantity restrictions. Measuring PCIe clock jitter is quick and easy with the Silicon Labs PCle Clock Jitter Tool. Download it for free at www.silabs.com/pcie-learningcenter.

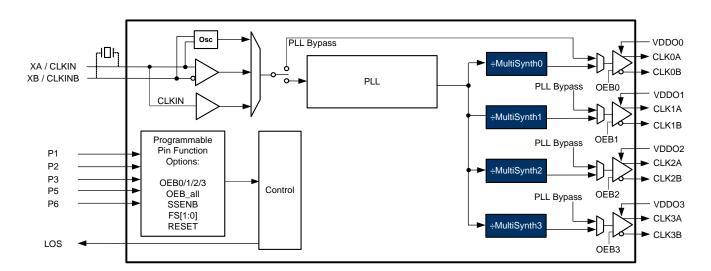

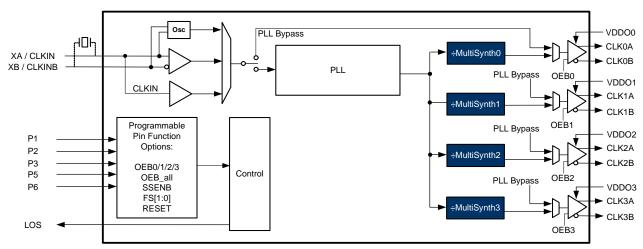

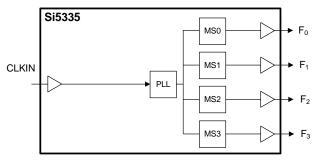

## **Functional Block Diagram**

## TABLE OF CONTENTS

| <u>Section</u>                                          | <u>Page</u> |

|---------------------------------------------------------|-------------|

| 1. Electrical Specifications                            | 4           |

| 2. Typical PCle System Diagram                          |             |

| 3. Functional Description                               | 17          |

| 3.1. Overview                                           | 17          |

| 3.2. MultiSynth Technology                              |             |

| 3.3. ClockBuilder Web-Customization Utility             | 18          |

| 3.4. Input Configuration                                |             |

| 3.5. Input and Output Frequency Configuration           | 23          |

| 3.6. Multi-Function Control Inputs                      | 23          |

| 3.7. Output Enable                                      |             |

| 3.8. Frequency Select/Device Reset                      | 24          |

| 3.9. Loss-of-Signal Alarm                               | 25          |

| 3.10. Output Stage                                      |             |

| 4. Power Consumption                                    |             |

| 5. Spread Spectrum                                      |             |

| 6. Jitter Performance                                   | _           |

| 7. Power Supply Considerations                          |             |

| 8. Loop Bandwidth Considerations                        |             |

| 9. Applications of the Si5335                           |             |

| 9.1. Free-Running Clock Generator                       |             |

| 9.2. Synchronous Frequency Translation                  |             |

| 9.3. Configurable Universal Buffer and Level Translator |             |

| 10. Pin Descriptions                                    |             |

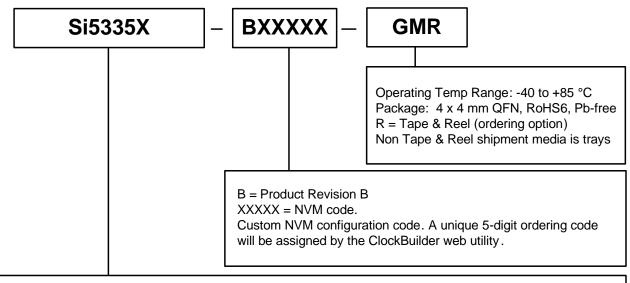

| 11. Ordering Information                                |             |

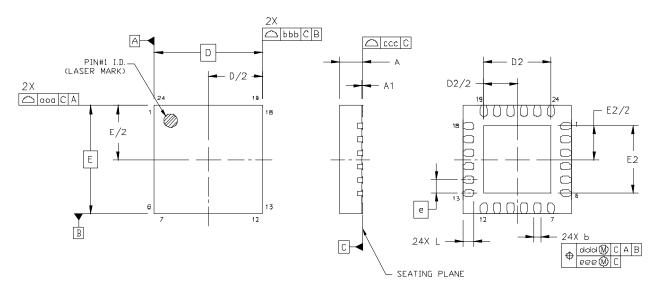

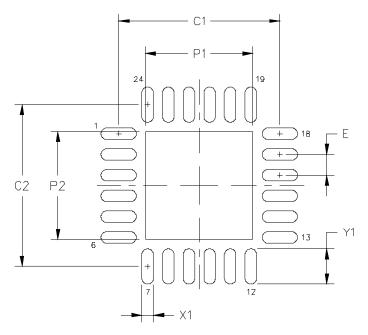

| 12. Package Outline: 24-Lead QFN                        |             |

| 13. Recommended PCB Land Pattern                        |             |

| 14. Top Marking                                         |             |

| 14.1. Si5335 Top Marking                                |             |

| 14.2. Top Marking Explanation                           |             |

| 15. Device Errata                                       | 45          |

| Document Change List                                    | 46          |

## 1. Electrical Specifications

**Table 1. Recommended Operating Conditions**

$(V_{DD} = 1.8 \text{ V} -5\% \text{ to } +10\%, 2.5 \text{ V} \pm 10\%, \text{ or } 3.3 \text{ V} \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                       | Symbol            | Test Condition | Min  | Тур | Max  | Unit |

|---------------------------------|-------------------|----------------|------|-----|------|------|

| Ambient Temperature             | T <sub>A</sub>    |                | -40  | 25  | 85   | °C   |

|                                 |                   |                | 2.97 | 3.3 | 3.63 | V    |

| Core Supply Voltage             | $V_{DD}$          |                | 2.25 | 2.5 | 2.75 | V    |

|                                 |                   |                | 1.71 | 1.8 | 1.98 | V    |

| Output Buffer Supply<br>Voltage | V <sub>DDOn</sub> |                | 1.4  | _   | 3.63 | V    |

**Note:** All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions. Typical values apply at nominal supply voltages and an operating temperature of 25 °C unless otherwise noted.

**Table 2. DC Characteristics**

( $V_{DD}$  = 1.8 V –5% to +10%, 2.5 V ±10%, or 3.3 V ±10%,  $T_A$  = –40 to 85 °C)

| Parameter                                     | Symbol            | Test Condition                                                    | Min | Тур | Max | Unit |

|-----------------------------------------------|-------------------|-------------------------------------------------------------------|-----|-----|-----|------|

| Core Supply Current<br>(Clock Generator Mode) | I <sub>DDCG</sub> | 100 MHz on all outputs,<br>25 MHz refclk,<br>clock generator mode | _   | 45  | 60  | mA   |

| Core Supply Current<br>(Buffer Mode)          | I <sub>DDB</sub>  | 50 MHz refclk                                                     | _   | 12  | _   | mA   |

|                                               |                   | LVPECL, 350 MHz                                                   | _   | _   | 30  | mA   |

|                                               |                   | CML, 350 MHz                                                      | _   | 12  | _   | mA   |

|                                               |                   | LVDS, 350 MHz                                                     | _   | _   | 8   | mA   |

|                                               |                   | HCSL, 250 MHz<br>2 pF load                                        | _   | _   | 20  | mA   |

|                                               |                   | SSTL, 350 MHz                                                     | _   | _   | 19  | mA   |

| Output Buffer Supply Current                  | I <sub>DDOx</sub> | CMOS, 50 MHz<br>15 pF load <sup>1</sup>                           | _   | 6   | 9   | mA   |

|                                               |                   | CMOS, 200 MHz <sup>1,2</sup><br>3.3 V VDD0                        | _   | 13  | 18  | mA   |

|                                               |                   | CMOS, 200 MHz <sup>1,2</sup><br>2.5 V                             | _   | 10  | 14  | mA   |

|                                               |                   | CMOS, 200 MHz <sup>1,2</sup><br>1.8 V                             | _   | 7   | 10  | mA   |

|                                               |                   | HSTL, 350 MHz                                                     | _   | _   | 19  | mA   |

#### Notes:

- 1. Single CMOS driver active.

- 2. Measured into a 5" 50  $\Omega$  trace with 2 pF load.

**Table 3. Performance Characteristics**

$(V_{DD} = 1.8 \ V - 5\% \ to + 10\%, 2.5 \ V \pm 10\%, or 3.3 \ V \pm 10\%, T_A = -40 \ to 85 \ ^{\circ}C)$

| Parameter                                              | Symbol              | Test Condition                       | Min  | Тур   | Max  | Unit |

|--------------------------------------------------------|---------------------|--------------------------------------|------|-------|------|------|

| PLL Acquisition Time                                   | t <sub>ACQ</sub>    | 1.6 MHz loop bandwidth               | _    |       | 25   | ms   |

| PLL Tracking Range                                     | f <sub>TRACK</sub>  | 475 kHz or 1.6 MHz loop<br>bandwidth | 5000 | 20000 | _    | ppm  |

| DLL Loop Bondwidth                                     | f <sub>BW1</sub>    | High bandwidth option                | _    | 1.6   | _    | MHz  |

| PLL Loop Bandwidth                                     | f <sub>BW2</sub>    | Low bandwidth option                 | _    | 475   | _    | kHz  |

| MultiSynth Frequency<br>Synthesis Resolution           | f <sub>RES</sub>    | Output frequency ≤ Fvco/8            | 0    | 0     | 1    | ppb  |

| CLKIN Loss of Signal Detect<br>Time                    | t <sub>LOS</sub>    |                                      | _    | 2.6   | 5    | μs   |

| CLKIN Loss of Signal Release<br>Time                   | t <sub>LOSRLS</sub> |                                      | 0.01 | 0.2   | 1    | μs   |

| POR to Output Clock Valid                              | t <sub>RDY</sub>    |                                      | _    | _     | 2    | ms   |

| Input-to-Output Propagation Delay                      | t <sub>PROP</sub>   | Buffer Mode<br>(PLL Bypass)          | _    | 2.5   | 4    | ns   |

| Reset Minimum Pulse Width                              | t <sub>RESET</sub>  |                                      | _    | _     | 200  | ns   |

| Output-Output Skew <sup>1</sup>                        | t <sub>DSKEW</sub>  | F <sub>OUT</sub> ≥ 5 MHz             | _    | _     | 100  | ps   |

| Spread Spectrum PP<br>Frequency Deviation <sup>2</sup> | SS <sub>DEV</sub>   | F <sub>OUT</sub> = 100 MHz           | _    | -0.45 | -0.5 | %    |

| Spread Spectrum Modulation Rate <sup>3</sup>           | SS <sub>DEV</sub>   | F <sub>OUT</sub> = 100 MHz           | 30   | 31.5  | 33   | kHz  |

|                                                        |                     |                                      |      |       |      |      |

- Outputs at integer-related frequencies and using the same driver format.

Default value is 0.5% down spread.

- **3.** Default value is 31.5 kHz for PCI compliance.

**Table 4. Input and Output Clock Characteristics**

$(V_{DD} = 1.8 \text{ V} - 5\% \text{ to } + 10\%, 2.5 \text{ V} \pm 10\%, \text{ or } 3.3 \text{ V} \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                     | Symbol                         | Test Condition                        | Min                          | Тур      | Max | Unit            |

|-------------------------------|--------------------------------|---------------------------------------|------------------------------|----------|-----|-----------------|

| Input Clock (AC Cou           | oled Diffe                     | rential Input Clocks o                | n Pins 1 and 2) <sup>1</sup> |          |     | 1               |

| Frequency                     | f <sub>IN</sub>                | LVDS, LVPECL,<br>HCSL, CML            | 10 <sup>2</sup>              | _        | 350 | MHz             |

| Differential Voltage<br>Swing | $V_{PP}$                       | 350 MHz input                         | 0.4                          | _        | 2.4 | V <sub>PP</sub> |

| Rise/Fall Time <sup>3</sup>   | t <sub>R</sub> /t <sub>F</sub> | 20%-80%                               | _                            | _        | 1.0 | ns              |

|                               | DC<br>(PLL<br>mode)            | < 1 ns t <sub>R</sub> /t <sub>F</sub> | 40                           | _        | 60  | %               |

| Duty Cycle <sup>3</sup> [(I   | DC<br>(PLL<br>bypass<br>mode)  | < 1 ns t <sub>R</sub> /t <sub>F</sub> | 45                           | _        | 55  | %               |

| Input Impedance <sup>1</sup>  | R <sub>IN</sub>                |                                       | 10                           | _        | _   | kΩ              |

| Input Capacitance             | C <sub>IN</sub>                |                                       | _                            | 3.5      | _   | pF              |

| Input Clock (AC-Cou           | pled Sing                      | le-Ended Input Clock                  | on Pin 1)                    | <u>.</u> |     | <u>"</u>        |

| Frequency                     | f <sub>IN</sub>                | CMOS, HSTL, SSTL                      | 10 <sup>2</sup>              | _        | 200 | MHz             |

| CMOS Input Voltage<br>Swing   | V <sub>I</sub>                 | 200 MHz                               | 0.8                          | _        | 1.2 | Vpp             |

| CMOS Rise/Fall Time           | t <sub>R</sub> /t <sub>F</sub> | 10%–90%                               | _                            | _        | 4   | ns              |

| CMOS Rise/Fall Time           | t <sub>R</sub> /t <sub>F</sub> | 20%-80%                               | _                            | _        | 2.3 | ns              |

| HSTL/SSTL Input<br>Voltage    | V <sub>I(HSTL/</sub><br>SSTL)  | 200 MHz                               | 0.4                          | _        | 1.2 | V <sub>PP</sub> |

| HSTL/SSTL Rise/Fall<br>Time   | t <sub>R</sub> /t <sub>F</sub> | 10%–90%                               |                              |          | 1.4 | ns              |

#### Notes:

- 1. Use an external 100  $\Omega$  resistor to provide load termination for a differential clock. See "3.4.2. Differential Input Clocks" on page 19.

- 2. Minimum input frequency in clock buffer mode (PLL bypass) is 5 MHz. Operation to 1 MHz is also supported in buffer mode, but loss-of-signal (LOS) status is not functional.

- 3. Applies to differential inputs. For best jitter performance, keep the midpoint peak-to-peak differential input slew rate on pins 1 and 2 faster than 0.3 V/ns.

- **4.** CML output format requires ac-coupling of the differential outputs to a differential 100  $\Omega$  load at the receiver. See "3.10.6. CML Outputs" on page 31.

- **5.** Includes effect of internal series  $22 \Omega$  resistor.

**Table 4. Input and Output Clock Characteristics (Continued)**

$(V_{DD} = 1.8 \text{ V} -5\% \text{ to } +10\%, 2.5 \text{ V} \pm 10\%, \text{ or } 3.3 \text{ V} \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                       | Symbol                         | Test Condition                           | Min   | Тур                          | Max   | Unit            |

|---------------------------------|--------------------------------|------------------------------------------|-------|------------------------------|-------|-----------------|

|                                 | DC<br>(PLL<br>mode)            | < 1 ns t <sub>R</sub> /t <sub>F</sub>    | 40    | _                            | 60    | %               |

| Duty Cycle                      | DC<br>(PLL<br>bypass<br>mode)  | < 1 ns t <sub>R</sub> /t <sub>F</sub>    | 45    | _                            | 55    | %               |

| Input Capacitance               | C <sub>IN</sub>                |                                          | _     | 3.5                          | _     | pF              |

| Output Clocks (Differ           | rential)                       |                                          |       |                              |       | "               |

| Fragues av                      |                                | LVPECL, LVDS, CML                        | 1     | _                            | 350   | MHz             |

| Frequency                       | f <sub>OUT</sub>               | HCSL                                     | 1     | _                            | 250   | MHz             |

| LVPECL                          | V <sub>OC</sub>                | common mode                              | _     | V <sub>DDO</sub> -<br>1.45 V | _     | V               |

| Output Voltage                  | V <sub>SEPP</sub>              | peak-to-peak single-<br>ended swing      | 0.55  | 0.8                          | 0.96  | V <sub>PP</sub> |

| LVDC Output Valtage             | V <sub>OC</sub>                | common mode                              | 1.125 | 1.2                          | 1.275 | V               |

| LVDS Output Voltage (2.5/3.3 V) | V <sub>SEPP</sub>              | peak-to-peak single-<br>ended swing      | 0.25  | 0.35                         | 0.45  | V <sub>PP</sub> |

| LVDS Output                     | V <sub>OC</sub>                | common mode                              | 0.8   | 0.875                        | 0.95  | V               |

| Voltage (1.8 V)                 | V <sub>SEPP</sub>              | peak-to-peak single-<br>ended swing      | 0.25  | 0.35                         | 0.45  | V <sub>PP</sub> |

|                                 | V <sub>OC</sub>                | common mode                              | 0.35  | 0.375                        | 0.400 | V               |

| HCSL Output Voltage             | V <sub>SEPP</sub>              | peak-to-peak single-<br>ended swing      | 0.575 | 0.725                        | 0.85  | V <sub>PP</sub> |

|                                 | V <sub>OC</sub>                | Common Mode                              | _     | See Note <sup>4</sup>        | _     | V               |

| CML Output Voltage              | V <sub>SEPP</sub>              | Peak-to-Peak Single-<br>ended Swing      | 0.67  | 0.860                        | 1.07  | V <sub>PP</sub> |

| Rise/Fall Time                  | t <sub>R</sub> /t <sub>F</sub> | 20% to 80%<br>LVPECL, LVDS,<br>HCSL, CML | _     | _                            | 450   | ps              |

#### Notes:

- 1. Use an external 100  $\Omega$  resistor to provide load termination for a differential clock. See "3.4.2. Differential Input Clocks" on page 19.

- 2. Minimum input frequency in clock buffer mode (PLL bypass) is 5 MHz. Operation to 1 MHz is also supported in buffer mode, but loss-of-signal (LOS) status is not functional.

- **3.** Applies to differential inputs. For best jitter performance, keep the midpoint peak-to-peak differential input slew rate on pins 1 and 2 faster than 0.3 V/ns.

- **4.** CML output format requires ac-coupling of the differential outputs to a differential 100  $\Omega$  load at the receiver. See "3.10.6. CML Outputs" on page 31.

- 5. Includes effect of internal series 22  $\Omega$  resistor.

#### **Table 4. Input and Output Clock Characteristics (Continued)**

$(V_{DD} = 1.8 \text{ V} - 5\% \text{ to } + 10\%, 2.5 \text{ V} \pm 10\%, \text{ or } 3.3 \text{ V} \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                               | Symbol                         | Test Condition             | Min            | Тур  | Max            | Unit |

|-----------------------------------------|--------------------------------|----------------------------|----------------|------|----------------|------|

| Duty Cycle                              | DC                             | LVPECL, LVDS,<br>HCSL, CML | 45             | _    | 55             | %    |

| Output Clocks (Sing                     | le-Ended)                      |                            |                |      |                |      |

| Fraguanay                               | f                              | CMOS                       | 1              | _    | 200            | MHz  |

| Frequency                               | f <sub>OUT</sub>               | SSTL, HSTL                 | 1              | _    | 350            | MHz  |

| CMOS 20%-80%<br>Rise/Fall Time          | t <sub>R</sub> /t <sub>F</sub> | 2 pF load                  | _              | 0.45 | 0.85           | ns   |

| CMOS 20%-80%<br>Rise/Fall Time          | t <sub>R</sub> /t <sub>F</sub> | 15 pF load                 | _              | _    | 2.0            | ns   |

| CMOS                                    | V <sub>OH</sub>                | 4 mA load                  | VDDO – 0.3     | _    |                | V    |

| Output Voltage <sup>5</sup>             | V <sub>OL</sub>                | 4 mA load                  |                | _    | 0.3            | V    |

| CMOS<br>Output Resistance <sup>5</sup>  |                                |                            | _              | 50   | _              | Ω    |

| HSTL, SSTL<br>20%–80%<br>Rise/Fall Time | t <sub>R</sub> /t <sub>F</sub> | See Figure 16.             | _              | 0.35 | _              | ns   |

| HSTL Output Voltage                     | V <sub>OH</sub>                | VDDO = 1.4 to 1.6 V        | 0.5xVDDO+0.3   | _    | _              | V    |

| 1131L Output Voltage                    | V <sub>OL</sub>                | VDDO = 1.4 to 1.6 V        | _              | _    | 0.5xVDDO -0.3  | V    |

|                                         | V <sub>OH</sub>                | SSTL-3                     | 0.45xVDDO+0.41 | _    | _              | V    |

|                                         | V <sub>OL</sub>                | VDDOx = 2.97 to<br>3.63 V  | _              | _    | 0.45xVDDO-0.41 | V    |

| SSTL Output Voltage                     | V <sub>OH</sub>                | SSTL-2 VDDOx =             | 0.5xVDDO+0.41  | _    | _              | V    |

| SSTE Output voltage                     | V <sub>OL</sub>                | 2.25 to 2.75 V             | _              | _    | 0.5xVDDO-0.41  | V    |

|                                         | V <sub>OH</sub>                | SSTL-18                    | 0.5xVDDO+0.34  | _    |                | V    |

|                                         | V <sub>OL</sub>                | VDDOx = 1.71 to<br>1.98 V  | _              | _    | 0.5xVDDO-0.34  | V    |

| HSTL, SSTL<br>Output Resistance         |                                |                            | _              | 50   | _              | Ω    |

| Duty Cycle                              | DC                             |                            | 45             | _    | 55             | %    |

#### Notes:

- 1. Use an external 100  $\Omega$  resistor to provide load termination for a differential clock. See "3.4.2. Differential Input Clocks" on page 19.

- 2. Minimum input frequency in clock buffer mode (PLL bypass) is 5 MHz. Operation to 1 MHz is also supported in buffer mode, but loss-of-signal (LOS) status is not functional.

- **3.** Applies to differential inputs. For best jitter performance, keep the midpoint peak-to-peak differential input slew rate on pins 1 and 2 faster than 0.3 V/ns.

- 4. CML output format requires ac-coupling of the differential outputs to a differential 100  $\Omega$  load at the receiver. See "3.10.6. CML Outputs" on page 31.

- **5.** Includes effect of internal series  $22 \Omega$  resistor.

Table 5. Control Pins\* ( $V_{DD}$  = 1.8 V -5% to +10%, 2.5 V ±10%, or 3.3 V ±10%,  $T_A$  = -40 to 85 °C)

| Parameter                                 | Symbol                         | Condition                                          | Min                   | Тур | Max                   | Unit |  |  |  |

|-------------------------------------------|--------------------------------|----------------------------------------------------|-----------------------|-----|-----------------------|------|--|--|--|

| Input Control Pins (P1, P2, P3, P5*, P6*) |                                |                                                    |                       |     |                       |      |  |  |  |

| Innut Valtage Laur                        | V                              | Pins P1, P2, P3                                    | -0.1                  | _   | 0.3 x V <sub>DD</sub> | V    |  |  |  |

| Input Voltage Low                         | $V_{IL}$                       | Pins P5 and P6                                     | _                     | _   | 0.3                   | V    |  |  |  |

| Input Voltage High                        | \/                             | Pins P1, P2, P3                                    | 0.7 x V <sub>DD</sub> | _   | 3.73                  | V    |  |  |  |

|                                           | V <sub>IH</sub>                | Pins P5* and P6*                                   | 0.85                  | _   | 1.2                   | V    |  |  |  |

| Input Capacitance                         | C <sub>IN</sub>                |                                                    | _                     | _   | 4                     | pF   |  |  |  |

| Input Resistance                          | R <sub>IN</sub>                |                                                    | _                     | 20  | _                     | kΩ   |  |  |  |

| Output Control Pins (LOS, Pin 8           | 3)                             |                                                    |                       |     |                       |      |  |  |  |

| Output Voltage Low                        | V <sub>OL</sub>                | I <sub>SINK</sub> = 3 mA                           | 0                     | _   | 0.4                   | V    |  |  |  |

| Rise/Fall Time 20–80%                     | t <sub>R</sub> /t <sub>F</sub> | $C_L < 10 \text{ pf, pull up} = 1 \text{ k}\Omega$ | _                     | _   | 10                    | ns   |  |  |  |

| *Note: For more information, see "3.6     | 6.1. P5 and                    | P6 Input Control" on page 24.                      |                       |     |                       |      |  |  |  |

Table 6. Crystal Specifications for 25 MHz

| Parameter                               | Symbol            | Min | Тур | Max | Unit |

|-----------------------------------------|-------------------|-----|-----|-----|------|

| Crystal Frequency                       | f <sub>XTAL</sub> | _   | 25  | _   | MHz  |

| Load Capacitance (on-chip differential) | CL                | _   | 18  | _   | pF   |

| Crystal Output Capacitance              | c <sub>O</sub>    | _   | _   | 5   | pF   |

| Equivalent Series Resistance            | r <sub>ESR</sub>  | _   | _   | 100 | Ω    |

| Crystal Max Drive Level                 | d <sub>L</sub>    | 100 | _   | _   | μW   |

Table 7. Crystal Specifications for 27 MHz

| Parameter                               | Symbol            | Min | Тур | Max | Unit |

|-----------------------------------------|-------------------|-----|-----|-----|------|

| Crystal Frequency                       | f <sub>XTAL</sub> | _   | 27  | _   | MHz  |

| Load Capacitance (on-chip differential) | c <sub>L</sub>    | _   | 18  | _   | pF   |

| Crystal Output Capacitance              | c <sub>O</sub>    | _   | _   | 5   | pF   |

| Equivalent Series Resistance            | r <sub>ESR</sub>  | _   | _   | 75  | Ω    |

| Crystal Max Drive Level                 | d <sub>L</sub>    | 100 | _   | _   | μW   |

Table 8. Jitter Specifications, Clock Generator Mode (Loop Bandwidth = 1.6 MHz)<sup>1,2,3</sup>

$(V_{DD} = 1.8 \text{ V} -5\% \text{ to } +10\%, 2.5 \text{ V} \pm 10\%, \text{ or } 3.3 \text{ V} \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                                                   | Symbol            | Test Condition                                              | Min | Тур  | Max  | Unit     |

|-------------------------------------------------------------|-------------------|-------------------------------------------------------------|-----|------|------|----------|

| GbE Random Jitter<br>(12 kHz–20 MHz) <sup>4</sup>           | $J_GbE$           | CLKIN = 25 MHz<br>All CLKn at 125 MHz <sup>5</sup>          | _   | 0.7  | 1    | ps RMS   |

| GbE Random Jitter<br>(1.875–20 MHz)                         | $R_{JGbE}$        | CLKIN = 25 MHz<br>All CLKn at 125 MHz <sup>5</sup>          | _   | 0.38 | 0.79 | ps RMS   |

| OC-12 Random Jitter<br>(12 kHz–5 MHz)                       | J <sub>OC12</sub> | CLKIN = 19.44 MHz<br>All CLKn at<br>155.52 MHz <sup>5</sup> |     | 0.7  | 1    | ps RMS   |

| PCI Express 1.1 Common<br>Clocked (with spread<br>spectrum) |                   | Total Jitter <sup>6</sup>                                   | _   | 20.1 | 33.6 | ps pk-pk |

| PCI Express 2.1 Common                                      |                   | RMS Jitter <sup>6</sup> , 10 kHz to<br>1.5 MHz              | _   | 0.15 | 1.47 | ps RMS   |

| Clocked (no spread spectrum)                                |                   | RMS Jitter <sup>6</sup> , 1.5 MHz to 50 MHz                 | _   | 0.58 | 0.75 | ps RMS   |

| PCI Express 3.0 Common<br>Clocked (no spread<br>spectrum)   |                   | RMS Jitter <sup>6</sup>                                     | _   | 0.15 | 0.45 | ps RMS   |

| PCIe Gen 3 Separate<br>Reference No Spread,<br>SRNS         |                   | PLL BW of 2–4 or<br>2–5 MHz,<br>CDR = 10 MHz                | _   | 0.11 | 0.32 | ps RMS   |

| PCIe Gen 4,<br>Common Clock                                 |                   | PLL BW of 2–4 or<br>2–5 MHz,<br>CDR = 10 MHz                | _   | 0.15 | 0.45 | ps RMS   |

| Period Jitter                                               | $J_{PER}$         | N = 10,000 cycles <sup>7</sup>                              | _   | 10   | 30   | ps pk-pk |

#### Notes:

- 1. All jitter measurements apply for LVDS/HCSL/LVPECL/CML output format with a low noise differential input clock and are made with an Agilent 90804 oscilloscope. All RJ measurements use RJ/DJ separation.

- 2. All jitter data in this table is based upon all output formats being differential. When single-ended outputs are used, there is the potential that the output jitter may increase due to the nature of single-ended outputs. If your configuration implements any single-ended output and any output is required to have jitter less than 2 ps rms, contact Silicon Labs for support to validate your configuration and ensure the best jitter performance. In many configurations, CMOS outputs have little to no effect upon jitter.

- **3.** For best jitter performance, keep the single-ended clock input slew rates at pins 1 and 2 greater that 1.0 V/ns and the differential clock input slew rates greater than 0.3 V/ns.

- 4. D<sub>J</sub> for PCI and GbE is < 5 ps pp

- **5.** Output MultiSynth in Integer mode.

- **6.** All output clocks 100 MHz HCSL format. Jitter is from the PCIE jitter filter combination that produces the highest jitter. See AN562 for details. Jitter is mesured with the Intel Clock Jitter Tool, Ver.1.6.4.

- 7. For any output frequency  $\geq$  10 MHz.

- 8. Measured in accordance with JEDEC standard 65.

- **9.** Rj is multiplied by 14; estimate the pp jitter from Rj over 2<sup>12</sup> rising edges.

- 10. Gen 4 specifications based on the PCI-Express Base Specification 4.0 rev. 0.5.

- 11. Download the Silicon Labs PCIe Clock Jitter Tool at www.silabs.com/pcie-learningcenter.

Table 8. Jitter Specifications, Clock Generator Mode (Loop Bandwidth = 1.6 MHz) $^{1,2,3}$  (Continued) ( $V_{DD} = 1.8 \ V - 5\% \ to + 10\%, 2.5 \ V \pm 10\%, or 3.3 \ V \pm 10\%, T_A = -40 \ to 85 \ ^{\circ}C$ )

| Parameter                        | Symbol                   | Test Condition                                                                                   | Min | Тур | Max | Unit               |

|----------------------------------|--------------------------|--------------------------------------------------------------------------------------------------|-----|-----|-----|--------------------|

| Cycle-Cycle Jitter               | Jcc                      | N = 10,000 cycles<br>Output MultiSynth<br>operated in integer or<br>fractional mode <sup>7</sup> | _   | 9   | 29  | ps pk <sup>8</sup> |

| Random Jitter<br>(12 kHz–20 MHz) | R <sub>J</sub>           | Output and feedback<br>MultiSynth in integer or<br>fractional mode <sup>7</sup>                  | _   | 0.7 | 1.5 | ps RMS             |

|                                  | DJ                       | Output MultiSynth operated in fractional mode <sup>7</sup>                                       | _   | 3   | 15  | ps pk-pk           |

| Deterministic Jitter             | ٥                        | Output MultiSynth operated in integer mode <sup>7</sup>                                          | _   | 2   | 10  | ps pk-pk           |

| Total Jitter<br>(12 kHz–20 MHz)  | $T_J = D_J + 14xR_J$     | Output MultiSynth operated in fractional mode <sup>7</sup>                                       | _   | 13  | 36  | ps pk-pk           |

|                                  | (See Note <sup>9</sup> ) | Output MultiSynth operated in integer mode <sup>7</sup>                                          |     | 12  | 20  | ps pk-pk           |

#### Notes:

- 1. All jitter measurements apply for LVDS/HCSL/LVPECL/CML output format with a low noise differential input clock and are made with an Agilent 90804 oscilloscope. All RJ measurements use RJ/DJ separation.

- 2. All jitter data in this table is based upon all output formats being differential. When single-ended outputs are used, there is the potential that the output jitter may increase due to the nature of single-ended outputs. If your configuration implements any single-ended output and any output is required to have jitter less than 2 ps rms, contact Silicon Labs for support to validate your configuration and ensure the best jitter performance. In many configurations, CMOS outputs have little to no effect upon jitter.

- **3.** For best jitter performance, keep the single-ended clock input slew rates at pins 1 and 2 greater that 1.0 V/ns and the differential clock input slew rates greater than 0.3 V/ns.

- 4. D<sub>J</sub> for PCI and GbE is < 5 ps pp

- 5. Output MultiSynth in Integer mode.

- **6.** All output clocks 100 MHz HCSL format. Jitter is from the PCIE jitter filter combination that produces the highest jitter. See AN562 for details. Jitter is mesured with the Intel Clock Jitter Tool, Ver.1.6.4.

- **7.** For any output frequency  $\geq$  10 MHz.

- 8. Measured in accordance with JEDEC standard 65.

- **9.** Rj is multiplied by 14; estimate the pp jitter from Rj over 2<sup>12</sup> rising edges.

- **10.** Gen 4 specifications based on the PCI-Express Base Specification 4.0 rev. 0.5.

- 11. Download the Silicon Labs PCIe Clock Jitter Tool at www.silabs.com/pcie-learningcenter.

Table 9. Jitter Specifications, Clock Generator Mode (Loop Bandwidth = 475 kHz)<sup>1,2</sup>

$(V_{DD} = 1.8 \text{ V} -5\% \text{ to } +10\%, 2.5 \text{ V} \pm 10\%, \text{ or } 3.3 \text{ V} \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                                                   | Symbol             | Test Condition                                               | Min | Тур  | Max  | Unit     |

|-------------------------------------------------------------|--------------------|--------------------------------------------------------------|-----|------|------|----------|

| DSL Random Jitter<br>(10 kHz–400 kHz)                       | R <sub>JDSL1</sub> | CLKIN = 70.656 MHz<br>All CLKn at<br>70.656 MHz <sup>4</sup> | _   | 0.8  | 2    | ps RMS   |

| DSL Random Jitter<br>(100 kHz–10 MHz)                       | R <sub>JDSL2</sub> | CLKIN = 70.656 MHz<br>All CLKn at<br>70.656 MHz <sup>4</sup> | _   | 0.9  | 2    | ps RMS   |

| DSL Random Jitter<br>(10 Hz–30 MHz)                         | R <sub>JDSL3</sub> | CLKIN = 70.656 MHz<br>All CLKn at<br>70.656 MHz <sup>4</sup> | _   | 1.95 | 2.2  | ps RMS   |

| PCI Express 1.1<br>Common Clocked<br>(with spread spectrum) |                    | Total Jitter <sup>5</sup>                                    | _   | 20   | 34   | ps pk-pk |

| PCI Express 2.1<br>Common Clocked                           |                    | RMS Jitter <sup>5</sup> , 10 kHz to<br>1.5 MHz               | _   | 0.3  | 0.5  | ps RMS   |

| (no spread spectrum)                                        |                    | RMS Jitter <sup>5</sup> , 1.5 MHz to 50 MHz                  | _   | 0.5  | 1.0  | ps RMS   |

| PCI Express 3.0<br>Common Clocked<br>(no spread spectrum)   |                    | RMS Jitter <sup>5</sup>                                      | _   | 0.15 | 0.45 | ps RMS   |

| PCIe Gen 3 Separate<br>Reference No Spread,<br>SRNS         |                    | PLL BW of 2–4 or<br>2–5 MHz,<br>CDR = 10 MHz                 | _   | 0.11 | 0.32 | ps RMS   |

| PCIe Gen 4,<br>Common Clock                                 |                    | PLL BW of 2–4 or<br>2–5 MHz,<br>CDR = 10 MHz                 | _   | 0.15 | 0.45 | ps RMS   |

| Period Jitter                                               | J <sub>PER</sub>   | N = 10,000 cycles <sup>6</sup>                               | _   | 10   | 30   | ps pk-pk |

#### Notes:

- 1. All jitter measurements apply for LVDS/HCSL/LVPECL/CML output format with a low noise differential input clock and are made with an Agilent 90804 oscilloscope. All RJ measurements use RJ/DJ separation.

- 2. All jitter data in this table is based upon all output formats being differential. When single-ended outputs are used, there is the potential that the output jitter may increase due to the nature of single-ended outputs. If your configuration implements any single-ended output and any output is required to have jitter less than 2 ps rms, contact Silicon Labs for support to validate your configuration and ensure the best jitter performance. In many configurations, CMOS outputs have little to no effect upon jitter.

- 3.  $D_1$  for PCI and GbE is < 5 ps pp

- 4. Output MultiSynth in Integer mode.

- 5. All output clocks 100 MHz HCSL format. Jitter is from the PCIE jitter filter combination that produces the highest jitter. See AN562 for details. Jitter is mesured with the Intel Clock Jitter Tool, Ver.1.6.4.

- **6.** For any output frequency  $\geq$  5 MHz.

- 7. Measured in accordance with JEDEC standard 65.

- **8.** Rj is multiplied by 14; estimate the pp jitter from Rj over 2<sup>12</sup> rising edges.

- 9. Gen 4 specifications based on the PCI-Express Base Specification 4.0 rev. 0.5.

- 10. Download the Silicon Labs PCIe Clock Jitter Tool at www.silabs.com/pcie-learningcenter.

Table 9. Jitter Specifications, Clock Generator Mode (Loop Bandwidth = 475 kHz) $^{1,2}$  (Continued) ( $V_{DD}$  = 1.8 V -5% to +10%, 2.5 V ±10%, or 3.3 V ±10%,  $T_A$  = -40 to 85 °C)

| Parameter                        | Symbol                   | Test Condition                                                                                   | Min | Тур | Max | Unit               |

|----------------------------------|--------------------------|--------------------------------------------------------------------------------------------------|-----|-----|-----|--------------------|

| Cycle-Cycle Jitter               | J <sub>CC</sub>          | N = 10,000 cycles<br>Output MultiSynth<br>operated in integer or<br>fractional mode <sup>6</sup> | _   | 9   | 29  | ps pk <sup>7</sup> |

| Random Jitter<br>(12 kHz–20 MHz) | R <sub>J</sub>           | Output and feedback<br>MultiSynth in integer or<br>fractional mode <sup>6</sup>                  | _   | 1   | 2.5 | ps RMS             |

| Deterministic Jitter             | DJ                       | Output MultiSynth operated in fractional mode <sup>6</sup>                                       | _   | 3   | 15  | ps pk-pk           |

|                                  | <i>D</i> <sub>J</sub>    | Output MultiSynth operated in integer mode <sup>6</sup>                                          |     | 2   | 10  | ps pk-pk           |

| Total Jitter                     | $T_J = D_J + 14xR_J$     | Output MultiSynth operated in fractional mode <sup>6</sup>                                       |     | 13  | 36  | ps pk-pk           |

| (12 kHz–20 MHz)                  | (See Note <sup>8</sup> ) | Output MultiSynth operated in integer mode <sup>6</sup>                                          | _   | 15  | 30  | ps pk-pk           |

#### Notes:

- 1. All jitter measurements apply for LVDS/HCSL/LVPECL/CML output format with a low noise differential input clock and are made with an Agilent 90804 oscilloscope. All RJ measurements use RJ/DJ separation.

- 2. All jitter data in this table is based upon all output formats being differential. When single-ended outputs are used, there is the potential that the output jitter may increase due to the nature of single-ended outputs. If your configuration implements any single-ended output and any output is required to have jitter less than 2 ps rms, contact Silicon Labs for support to validate your configuration and ensure the best jitter performance. In many configurations, CMOS outputs have little to no effect upon jitter.

- 3.  $D_1$  for PCI and GbE is < 5 ps pp

- 4. Output MultiSynth in Integer mode.

- **5.** All output clocks 100 MHz HCSL format. Jitter is from the PCIE jitter filter combination that produces the highest jitter. See AN562 for details. Jitter is mesured with the Intel Clock Jitter Tool, Ver.1.6.4.

- **6.** For any output frequency  $\geq$  5 MHz.

- 7. Measured in accordance with JEDEC standard 65.

- **8.** Rj is multiplied by 14; estimate the pp jitter from Rj over 2<sup>12</sup> rising edges.

- 9. Gen 4 specifications based on the PCI-Express Base Specification 4.0 rev. 0.5.

- 10. Download the Silicon Labs PCIe Clock Jitter Tool at www.silabs.com/pcie-learningcenter.

Table 10. itter Specifications, Clock Buffer Mode (PLL Bypass)\*

$(V_{DD} = 1.8 \text{ V} -5\% \text{ to } +10\%, 2.5 \text{ V} \pm 10\%, \text{ or } 3.3 \text{ V} \pm 10\%, T_A = -40 \text{ to } 85^{\circ}\text{C})$

| Parameter                                                                                                                                                              | Symbol              | Test Condition                                                                  | Min   | Тур   | Max    | Unit   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------|-------|-------|--------|--------|

| Additive Phase Jitter<br>(12 kHz–20 MHz)                                                                                                                               | <sup>t</sup> RPHASE | 0.7 V pk-pk differential input<br>clock at 350 MHz with<br>70 ps rise/fall time | _     | 0.165 | _      | ps RMS |

| Additive Phase Jitter (50 kHz–80 MHz)  triangler (50 kHz–80 MHz)  triangler (50 kHz–80 MHz)  0.7 V pk-pk differential input clock at 350 MHz with 70 ps rise/fall time |                     | _                                                                               | 0.225 | _     | ps RMS |        |

\*Note: All outputs are in Clock Buffer mode (PLL Bypass).

**Table 11. Typical Phase Noise Performance**

| Offset<br>Frequency | Loop<br>Bandwidth | 25 MHz XTAL<br>to 156.25 MHz | 27 MHz Ref In<br>to 148.3517 MHz | 19.44 MHz Ref In<br>to 155.52 MHz | 100 MHz Ref In<br>to 100 MHz | Units  |

|---------------------|-------------------|------------------------------|----------------------------------|-----------------------------------|------------------------------|--------|

| 100 Hz              | 1.6 MHz           | -90                          | -87                              | -110                              | <b>–</b> 115                 | dBc/Hz |

|                     | 475 kHz           | N/A*                         | <b>-</b> 91                      | <b>–</b> 91                       | -113                         | dBc/Hz |

| 1 kHz               | 1.6 MHz           | -120                         | -117                             | -116                              | -122                         | dBc/Hz |

|                     | 475 kHz           | N/A*                         | -112                             | -111                              | -122                         | dBc/Hz |

| 10 kHz              | 1.6 MHz           | -126                         | -123                             | -123                              | -128                         | dBc/Hz |

|                     | 475 kHz           | N/A*                         | -124                             | -122                              | -127                         | dBc/Hz |

| 100 kHz             | 1.6 MHz           | -132                         | -130                             | -128                              | -136                         | dBc/Hz |

|                     | 475 kHz           | N/A*                         | -122                             | -121                              | -124                         | dBc/Hz |

| 1 MHz               | 1.6 MHz           | -132                         | -132                             | -128                              | -136                         | dBc/Hz |

|                     | 475 kHz           | N/A*                         | -133                             | -131                              | -135                         | dBc/Hz |

| 10 MHz              | 1.6 MHz           | -145                         | -145                             | -145                              | -152                         | dBc/Hz |

|                     | 475 kHz           | N/A*                         | -152                             | -153                              | -152                         | dBc/Hz |

| *Note: XTAL i       | nput mode doe     | s not support the 475        | kHz loop bandwidth               | setting.                          |                              |        |

**Table 12. Thermal Characteristics**

| Parameter                                 | Symbol        | Test Condition | Value | Unit |

|-------------------------------------------|---------------|----------------|-------|------|

| Thermal Resistance<br>Junction to Ambient | $\theta_{JA}$ | Still Air      | 37    | °C/W |

| Thermal Resistance<br>Junction to Case    | θЈС           | Still Air      | 25    | °C/W |

Table 13. Absolute Maximum Ratings<sup>1</sup>

| Parameter                                      | Symbol           | Test Condition                       | Value       | Unit      |

|------------------------------------------------|------------------|--------------------------------------|-------------|-----------|

| DC Supply Voltage                              | V <sub>DD</sub>  |                                      | -0.5 to 3.8 | V         |

| Input Voltage                                  | V <sub>IN</sub>  | Pins: XA/CLKIN,<br>XB/CLKINB, P5, P6 | -0.5 to 1.3 | V         |

|                                                |                  | Pins: P1, P2, P3                     | -0.5 to 3.8 | V         |

| Storage Temperature Range                      | T <sub>STG</sub> |                                      | -55 to 150  | °C        |

| ESD Tolerance                                  |                  | HBM<br>(100 pF, 1.5 kΩ)              | 2.5         | kV        |

| ESD Tolerance                                  |                  | CDM                                  | 550         | V         |

| ESD Tolerance                                  |                  | MM                                   | 175         | V         |

| Latch-up Tolerance                             |                  |                                      | JESD78 (    | Compliant |

| Junction Temperature                           | TJ               |                                      | 150         | °C        |

| Peak Soldering Reflow Temperature <sup>2</sup> |                  |                                      | 260         | °C        |

#### Notes:

- 1. Permanent device damage may occur if the absolute maximum ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Refer to JEDEC J-STD-020 standard for more information.

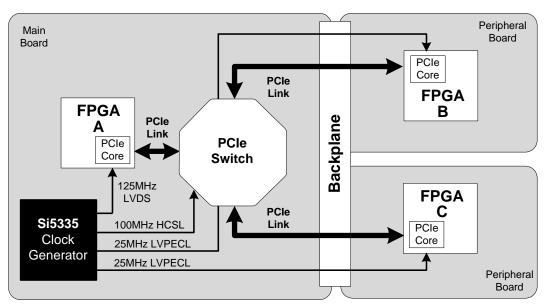

## 2. Typical PCIe System Diagram

Figure 1. PCI Express Switching Application Example

Figure 1 shows the Si5335 in a PCI Express application using the common clock topology. The Si5335 provides reference clocks to the three FPGAs, each of which requires a different clock signaling format (LVDS, LVPECL), I/O voltage (1.8, 2.5, 3.3 V), or frequency (25, 100, 125 MHz). In addition, the Si5335 provides a PCIe compliant, 100 MHz HCSL reference clock to the PCIe switch.

## 3. Functional Description

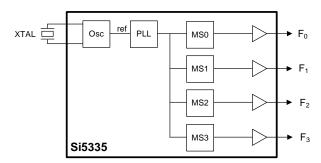

Figure 2. Si5335 Functional Block Diagram

#### 3.1. Overview

The Si5335 is a high-performance, low-jitter clock generator or buffer capable of synthesizing four independent user-programmable clock frequencies up to 350 MHz. The device supports free-run operation using an external 25 or 27 MHz crystal, or it can lock to an external clock for generating synchronous clocks. The output drivers support four differential clocks or eight single-ended clocks or a combination of both. The output drivers are configurable to support common signal formats, such as LVPECL, LVDS, HCSL, CML, CMOS, HSTL, and SSTL. Separate output supply pins allow supply voltages of 3.3, 2.5, 1.8, and 1.5 V to support the multi-format output driver. The core voltage supply accepts 3.3, 2.5, or 1.8 V and is independent from the output supplies. Using its two-stage synthesis architecture and patented high-resolution MultiSynth technology, the Si5335 can generate four independent frequencies from a single input frequency. In addition to clock generation, the inputs can bypass the synthesis stage enabling the Si5335 to be used as a high-performance clock buffer.

Spread spectrum\* is available on each of the clock outputs for EMI-sensitive applications, such as PCI Express. The device includes an interrupt pin that monitors for both loss of PLL lock (LOL) and loss of input signal (LOS) conditions while configured in clock generator mode. In clock generator mode, the LOS pin is asserted whenever LOL or LOS is true. In clock buffer mode (i.e., when the PLL is bypassed), the LOS pin is asserted whenever the input clock is lost. The LOL condition does not apply in clock buffer mode.

\*Note: See " Document Change List" on page 46 for more information.

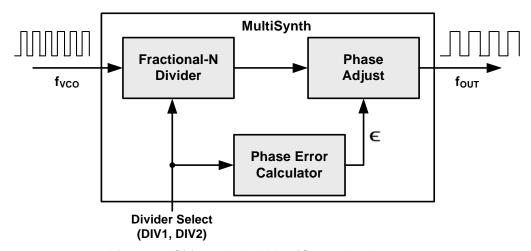

## 3.2. MultiSynth Technology

Next-generation timing architectures require a wide range of frequencies which are often non-integer related. Traditional clock architectures address this by using a combination of single PLL ICs, 4-PLL ICs and discrete XOs, often at the expense of BOM complexity and power. The Si5335 uses patented MultiSynth technology to dramatically simplify timing architectures by integrating the frequency synthesis capability of 4 phase-locked loops (PLLs) in a single device, greatly minimizing size and power requirements versus traditional solutions. Based on a fractional-N PLL, the heart of the architecture is a low phase noise, high-frequency VCO. The VCO supplies a high frequency output clock to the MultiSynth block on each of the four independent output paths. Each MultiSynth operates as a high-speed fractional divider with Silicon Laboratories' proprietary phase error correction to divide down the VCO clock to the required output frequency with very low jitter.

The first stage of the MultiSynth architecture is a fractional-N divider which switches seamlessly between the two closest integer divider values to produce the exact output clock frequency with 0 ppm error. To eliminate phase error generated by this process, MultiSynth calculates the relative phase difference between the clock produced by the fractional-N divider and the desired output clock and dynamically adjusts the phase to match the ideal clock waveform. This novel approach makes it possible to generate any output clock frequency without sacrificing jitter performance. Based on this architecture, the output of each MultiSynth can produce any frequency from 1 to 350 MHz.

Figure 3. Silicon Labs' MultiSynth Technology

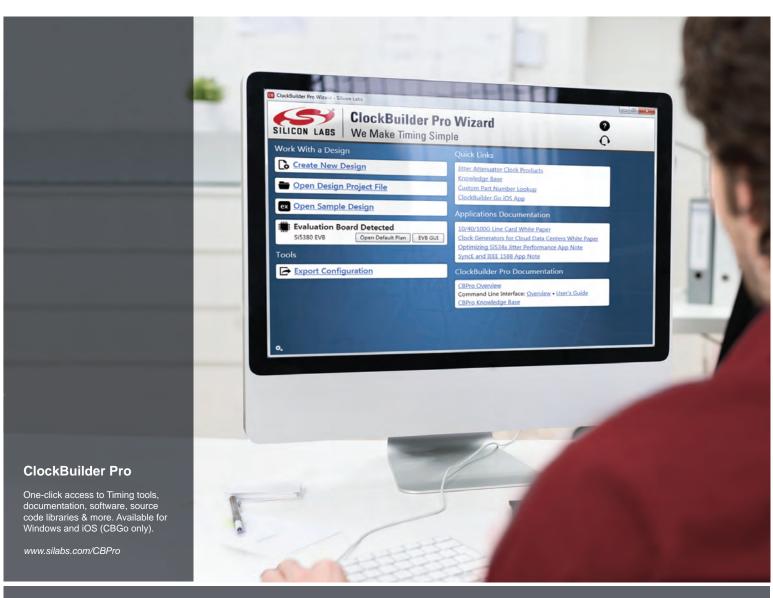

#### 3.3. ClockBuilder Web-Customization Utility

ClockBuilder is a web-based utility available at <a href="www.silabs.com/ClockBuilder">www.silabs.com/ClockBuilder</a> that allows hardware designers to tailor the Si5335's flexible clock architecture to meet any application-specific requirements and order custom clock samples. Through a simple point-and-click interface, users can specify any combination of input frequency and output frequencies and generate a custom part number for each application-specific configuration. There are no minimum order quantity restrictions.

ClockBuilder enables mass customization of clock generators. This allows a broader range of applications to take advantage of using application-specific pin controlled clocks, simplifying design while eliminating the firmware development required by traditional I<sup>2</sup>C-programmable clock generators.

Based on Silicon Labs' patented MultiSynth technology, the device PLL output frequency is constant and all clock output frequencies are synthesized by the four MultiSynth fractional dividers. All PLL parameters, including divider settings, VCO frequency, loop bandwidth, charge pump current, and phase margin are internally set by the device during the configuration process. This ensures optimized jitter performance and loop stability while simplifying design.

## 3.4. Input Configuration

The Si5335 input can be driven from either an external crystal or a reference clock. Reference selection is made when the device configuration is specified using the ClockBuilder™ web-based utility available at www.silabs.com/ClockBuilder.

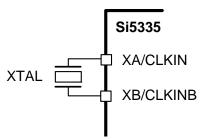

#### 3.4.1. Crystal Input

If the crystal input option is used, the Si5335 operates as a free-running clock generator. In this mode of operation the device requires a low-cost 25 or 27 MHz fundamental mode crystal connected across XA and XB as shown in Figure 4. Given the Si5335's frequency flexibility, the same 25 or 27 MHz crystal can be reused to generate any combination of output frequencies. Custom frequency crystals are not required. The Si5335 integrates the crystal load capacitors on-chip to reduce external component count. The crystal should be placed very close to the device to minimize stray capacitance. To ensure stable oscillation, the recommended crystal specifications provided in Tables 6 and 7 must be followed. See AN360 for additional details regarding crystal recommendations.

Figure 4. Connecting an XTAL to the Si5335

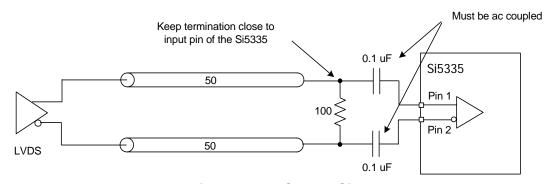

#### 3.4.2. Differential Input Clocks

The multi-format differential clock inputs of the Si5335 will interface with today's most common differential signals, such as LVDS, LVPECL, CML, and HCSL. The differential inputs are internally self-biased and must be ac-coupled externally with a  $0.1\,\mu\text{F}$  capacitor. The receiver will accept a signal with a voltage swing between 400 mV and  $2.4\,\text{V}_{PP}$  differential. Each half of the differential signal must not exceed  $1.2\,\text{V}_{PP}$  at the input to the Si5335 or else the  $1.3\,\text{V}$  dc voltage limit may be exceeded.

#### 3.4.2.1. LVDS Inputs

When interfacing the Si5335 device to an LVDS signal, a 100  $\Omega$  termination is required at the input along with the required dc blocking capacitors as shown in Figure 5.

Figure 5. LVDS Input Signal

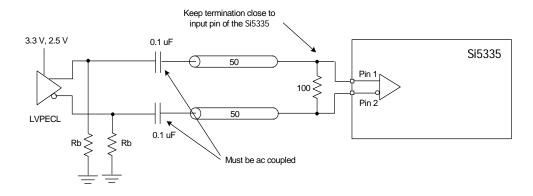

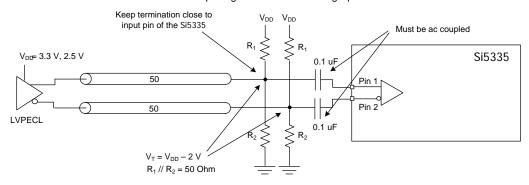

#### 3.4.2.2. LVPECL Input Clocks

Recommended configurations for interfacing an LVPECL input signal to the Si5335 are shown in Figure 6. Typical values for the bias resistors (Rb) range between 120 and 200  $\Omega$  depending on the LVPECL driver. The 100  $\Omega$  resistor provides line termination. Because the receiver is internally self-biased, no additional external bias is required.

Another solution is to terminate the LVPECL driver with a Thevenin configuration as shown in Figure 6b. The

values for R<sub>1</sub> and R<sub>2</sub> are calculated to provide a  $50\Omega$  termination to V<sub>DD</sub>-2V. Given this, the recommended resistor values are R<sub>1</sub> = 127  $\Omega$  and R<sub>2</sub> = 82.5  $\Omega$  for V<sub>DD</sub> = 3.3 V, and R<sub>1</sub> = 250  $\Omega$  and R<sub>2</sub> = 62.5  $\Omega$  for V<sub>DD</sub> = 2.5 V.

LVPECL Input Signal with Source Biasing Option

LVPECL Input Signal with Load Biasing Option

Figure 6. Recommended Options for Interfacing to an LVPECL Input Signal

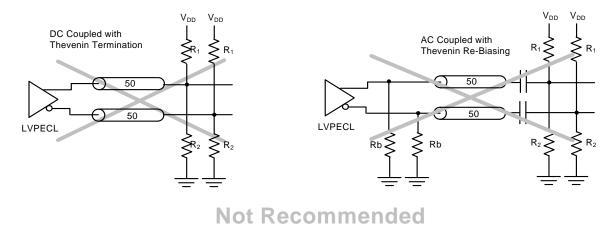

Since the differential receiver of the Si5335 is internally self biased, an LVPECL signal may not be dc-coupled to the device. Figure 7 shows some common LVPECL connections that should not be used because of the dc levels they present at the receiver's input.

Figure 7. Common LVPECL Connections that May be Destructive to the Si5335 Input

SHIPPN LADS

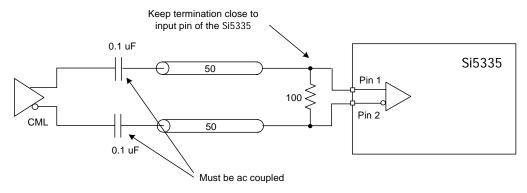

#### 3.4.2.3. CML Input Clocks

CML signals may be applied to the differential inputs of the Si5335. Since the Si5335 differential inputs are internally self-biased, a CML signal may not be dc-coupled to the device.

The recommended configurations for interfacing a CML input signal to the Si5335 are shown in Figure 8. The 100  $\Omega$  resistor provides line termination, and, since the receiver is internally-biased, no additional external biasing components are required.

Figure 8. CML Input Signal

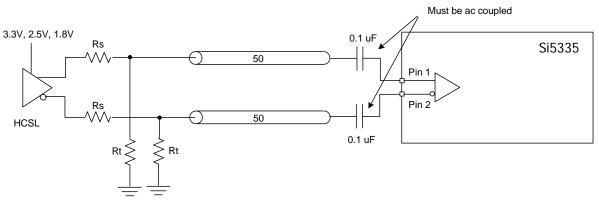

## 3.4.2.4. HCSL Input Clocks

A typical HCSL driver has an open source output, which requires an external series resistor and a resistor to ground. The values of these resistors depend on the driver but are typically equal to  $33\,\Omega$  (Rs) and  $50\,\Omega$  (Rt). Note that the HCSL driver in the Si5335 requires neither Rs nor Rt resistors. Other than two ac-coupling capacitors, no additional external components are necessary when interfacing an HCSL signal to the Si5335.

Figure 9. HCSL Input Signal to Si5335

#### 3.4.3. Single-Ended CMOS Input Clocks

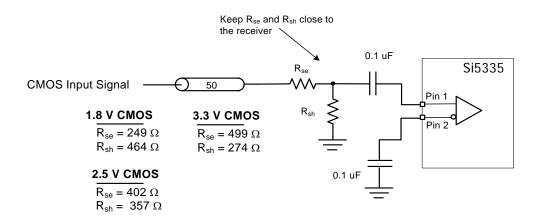

For synchronous timing applications, the Si5335 can lock to a 10 to 200 MHz CMOS reference clock. A typical interface circuit is shown in Figure 10. A series termination resistor may be required if the CMOS driver impedance does not match the trace impedance.

Figure 10. Interfacing CMOS Reference Clocks to the Si5335

## 3.4.4. Single-Ended SSTL and HSTL Input Clocks

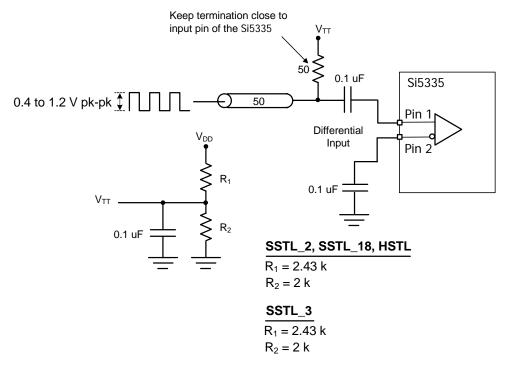

HSTL and SSTL single-ended inputs can be input to the differential inputs, pins 1 and 2, of the Si5335 with the circuit shown in Figure 11.

Some drivers may require a series 25  $\Omega$  resistor. If the SSTL/HSTL input is being driven by another Si5335 device, the 25  $\Omega$  series resistor is not required as this is integrated on-chip. The maximum recommended input frequency in this case is 350 MHz.

Figure 11. Single-Ended SSTL/HSTL Input Clocks to the Si5335

#### 3.4.5. Applying a Single-Ended Clock to the Differential Input Clock Pins

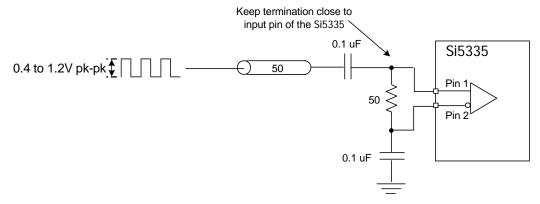

It is possible to interface any single-ended clock signal to the differential input pins (XA/CLKIN, XB/CLKINB). The recommended interface for a signal that requires a 50  $\Omega$  load is shown in Figure 12. On these inputs, it is important that the signal level be less than 1.2  $V_{PP}$  SE and greater than 0.4  $V_{PP}$  SE. The maximum recommended input frequency in this case is 350 MHz.

Figure 12. Single-Ended Input Signal with 50  $\Omega$  Termination

## 3.5. Input and Output Frequency Configuration

The Si5335 utilizes a single PLL-based architecture, four independent MultiSynth fractional output dividers, and a MultiSynth fractional feedback divider such that a single device provides the clock generation capability of 4 independent PLLs. Unlike competitive multi-PLL solutions, the Si5335 can generate four unique non-integer related output frequencies with 0 ppm frequency error for any combination of output frequencies. In addition, any combination of output frequencies can be generated from a single reference frequency without having to change the crystal or reference clock frequency between frequency configurations.

The Si5335 frequency configuration is set when the device configuration is specified using the ClockBuilder webbased utility available at <a href="https://www.silabs.com/ClockBuilder">www.silabs.com/ClockBuilder</a>. Any combination of output frequencies ranging from 1 to 350 MHz can be configured on each of the device outputs. Up to three unique device configurations can be specified in a single device, enabling the Si5335 to replace 3 different clock generators or clock buffers.

## 3.6. Multi-Function Control Inputs

The Si5335 supports five user-defined input pins (pins 3, 5, 6, 12, 19) that are customizable to support the functions listed below. The pinout of each device is customized using the ClockBuilder utility. This enables the device to be custom tailored to a specific application. Each of the different functions is described in further detail below.

| Pin Function | Description                   | Assignable Pin Name  |

|--------------|-------------------------------|----------------------|

| OEB_all      | Output Enable All.            | P1, P2, P3, P5*, P6* |

|              | All outputs enabled when low. |                      |

| OEB0         | Output Enable Bank 0.         | P1, P2, P3, P5*, P6* |

|              | CLK0A/0B enabled when low.    |                      |

| OEB1         | Output Enable Bank 1.         | P1, P2, P3, P5*, P6* |

|              | CLK1A/1B enabled when low.    |                      |

| OEB2         | Output Enable Bank 2.         | P1, P2, P3, P5*, P6* |

|              | CLK2A/2B enabled when low.    |                      |

| OEB3         | Output Enable Bank 3.         | P1, P2, P3, P5*, P6* |

|              | CLK3A/3B enabled when low.    |                      |

**Table 14. Multi-Function Control Inputs**

**Table 14. Multi-Function Control Inputs (Continued)**

| FS0   | Frequency Select.                                                                                                                     | P1                      |

|-------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|       | Selects active device frequency plan from factory-configured profiles. See "3.8. Frequency Select/Device Reset" for more information. |                         |

| FS1   | Frequency Select.                                                                                                                     | P1 (for 2-plan devices) |

|       | Selects active device frequency plan from factory-configured profiles. See "3.8. Frequency Select/Device Reset" for more information. | P2 (for 3-plan devices) |

| RESET | Reset.                                                                                                                                | P1, P2, P3              |

|       | Asserting this pin (driving high) is required to change FS1,FS0 pin setting. Reset is not required if FS1,FS0 pins are unassigned.    |                         |

| SSENB | Spread Spectrum Enable.                                                                                                               | P1, P2, P3, P5*, P6*    |

|       | Enables PCI-compliant spread spectrum clocking on all 100 MHz clock outputs when low.                                                 |                         |

#### 3.6.1. P5 and P6 Input Control

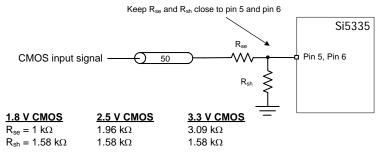

Control input signals to P5 and P6 cannot exceed 1.2 V. When these inputs are driven from CMOS sources, a resistive attenuator is required for pins 5 and 6, as shown in Figure 13.

Figure 13. P5, P6 Control Pin Termination

#### 3.7. Output Enable

24

Each of the device's four banks of clock outputs can be individually disabled using OEB0, OEB1, OEB2 and OEB3, respectively. Alternatively, all clock outputs can be disabled using the master output enable OEB\_all. When a Si5335 clock output bank is disabled, the output disable state is determined by the configuration specified in the ClockBuilder web utility. When one or more banks of clock outputs are enabled or disabled, clock start and stop transitions are handled glitchlessly.

#### 3.8. Frequency Select/Device Reset

The device frequency plan is customized using the ClockBuilder web utility. The Si5335 optionally supports up to three unique, pin-selectable configurations per device, enabling one device to replace up to three separate clock ICs. To select a particular frequency plan, set the FS pins as outlined below:

For custom Si5335 devices configured to support two frequency plans, the FS1 pin should be set as follows:

| 0 | 1 |

|---|---|

| 1 | 2 |

For custom Si5335 devices configured to support three frequency plans, the FS1 and FS0 pins should be set as follows:

| FS1 | FS0 | Profile  |

|-----|-----|----------|

| 0   | 0   | Reserved |

| 0   | 1   | 1        |

| 1   | 0   | 2        |

| 1   | 1   | 3        |

If a change is made to the FS pin settings, the device reset pin (RESET) must be held high for the minimum pulse width specified in Table 3 on page 5 to change the device configuration. The output clocks will be momentarily squelched until the device begins operation with the new frequency plan.

If the RESET pin is not selected in ClockBuilder as one of the five programmable pins, a power-on reset must be applied for an FS pin change to take effect.

## 3.9. Loss-of-Signal Alarm

The Si5335 supports a loss of signal (LOS) output indicator for monitoring the condition of the crystal/clock reference input. The LOS condition occurs when there is no input clock to the device or the PLL has lost lock (in clock generator mode). When an input clock is removed, the LOS pin will assert and the output clocks may drift up to 5% (in clock generator mode). When the input clock with an appropriate frequency is reapplied, the LOS pin will deassert. In clock buffer mode, LOS is driven high when the input clock is lost.

| LOS Output State | Description                 |

|------------------|-----------------------------|

| 0                | Input clock present and     |

|                  | PLL is locked               |

| 1                | Input clock not present and |

|                  | PLL is not locked           |

#### 3.10. Output Stage

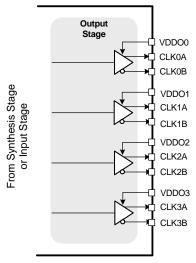

The output stage consists of programmable output drivers as shown in Figure 14.

Figure 14. Output Stage

The Si5335 devices provide four outputs that can be differential or single-ended. When configured as single-ended, the driver generates two signals that can be configured as in-phase or complementary. Each of the outputs has its own output supply pin, allowing the device to be used in mixed supply applications without the need for external level translators. The CML output driver generates a similar output swing as the LVPECL driver but consumes half the current. CML outputs must be ac-coupled.

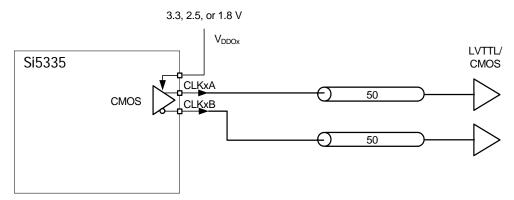

#### 3.10.1. CMOS/LVTTL Outputs

The CMOS output driver has a controlled impedance of about  $50~\Omega$ , which includes an internal series resistor of approximately  $22~\Omega$ . For this reason, an external Rs series resistor is not recommended when driving  $50~\Omega$  traces. If the trace impedance is higher than  $50~\Omega$ , a series resistor, Rs, should be used. A typical configuration is shown in Figure 15. A CMOS output driver can be configured with ClockBuilder as a single- or dual-output driver. Dual otuput configurations support in-phase or complementary outputs. The output supports 3.3, 2.5, and 1.8~V~CMOS signal levels when the appropriate voltage is supplied to the external VDDO pin and the device is configured accordingly.

Figure 15. Interfacing to a CMOS Receiver

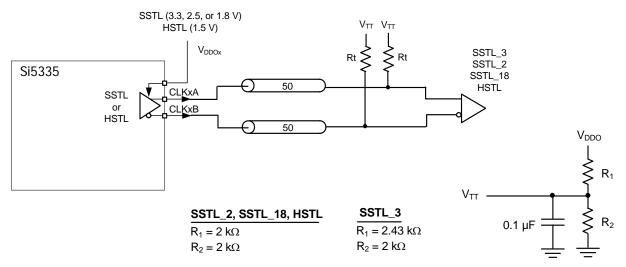

#### 3.10.2. SSTL and HSTL Outputs

The Si5335 supports both SSTL and HSTL outputs, which can be single-ended or differential. The recommended termination scheme for SSTL is shown in Figure 16. The  $V_{TT}$  supply can be generated using a simple voltage divider as shown below (note that Rt = 50  $\Omega$ ).

Figure 16. Interfacing the Si5335 to an SSTL or HSTL Receiver

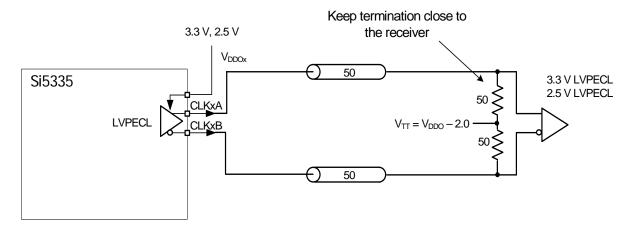

#### 3.10.3. LVPECL Outputs

The LVPECL driver is configurable in both 3.3 V or 2.5 V standard LVPECL modes. The output driver can be accoupled or dc-coupled to the receiver.

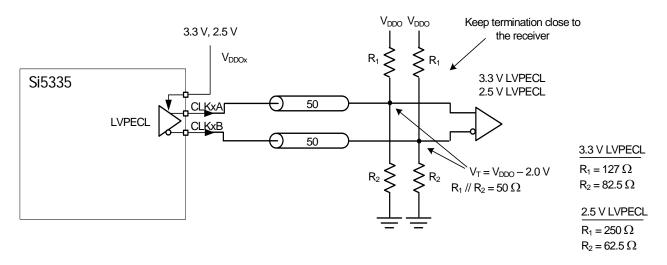

#### 3.10.3.1. DC-Coupled LVPECL Outputs

The standard LVPECL driver supports two commonly used dc-coupled configurations. Both of these are shown in Figure 17a and Figure 17b. LVPECL drivers were designed to be terminated with 50  $\Omega$  to VDD–2 V, which is illustrated in Figure 17a.  $V_{TT}$  can be supplied with a simple voltage divider as shown.

An alternative method of terminating LVPECL is shown in Figure 17b, which is the Thevenin equivalent to the termination in Figure 17a. It provides a 50  $\Omega$  load terminated to  $V_{DD}$ –2.0 V. For 3.3 V LVPECL, use  $R_1$  = 127  $\Omega$  and  $R_2$  = 82.5  $\Omega$ ; for 2.5 V LVPECL, use  $R_1$  = 250  $\Omega$  and  $R_2$  = 62.5  $\Omega$ . The only disadvantage to this type of termination is that the Thevenin circuit consumes additional power from the  $V_{DDO}$  supply.

a. DC-Coupled Termination of 50  $\Omega$  to  $V_{DDO}$  – 2.0 V

b. DC-Coupled with Thevenin Termination

Figure 17. Interfacing the Si5335 to an LVPECL Receiver Using DC Coupling

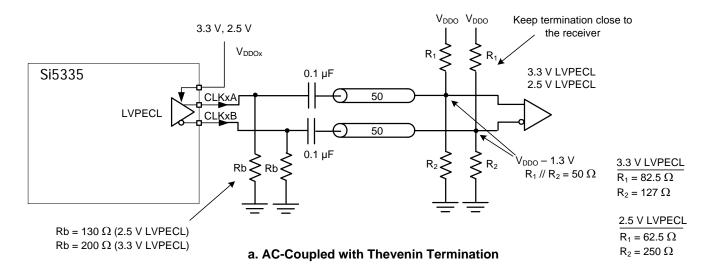

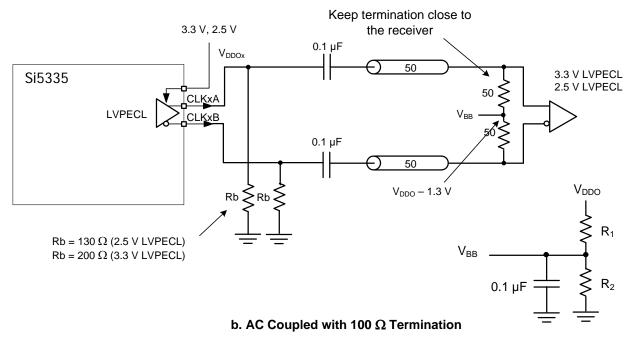

#### 3.10.3.2. AC Coupled LVPECL Outputs

AC coupling is necessary when a receiver and a driver have compatible voltage swings but different common-mode voltages. AC coupling works well for dc-balanced signals, such as for 50% duty cycle clocks. Figure 18 describes two methods for ac coupling the standard LVPECL driver. The Thevenin termination shown in Figure 18a is a convenient and common approach when a  $V_{BB}$  ( $V_{DD}$  – 1.3 V) supply is not available; however, it does consume additional power. The termination method shown in Figure 18b consumes less power. A  $V_{BB}$  supply can be generated from a simple voltage divider circuit as shown in Figure 18b.

Figure 18. Interfacing to an LVPECL Receiver Using AC Coupling

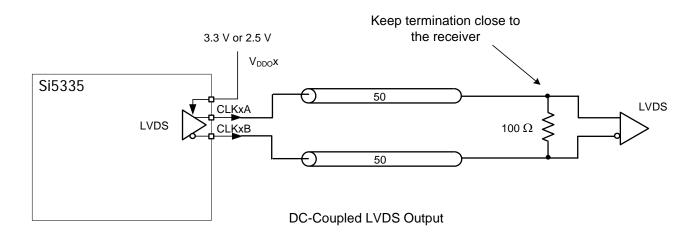

#### 3.10.4. LVDS Outputs

The LVDS output option provides a very simple and power-efficient interface that requires no external biasing when connected to an LVDS receiver. An ac-coupled LVDS driver is often useful as a CML driver. The LVDS driver may be dc-coupled or ac-coupled to the receiver in 3.3 V or 2.5 V output mode.

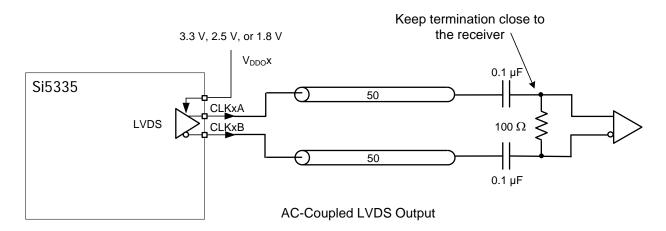

#### 3.10.4.1. AC-Coupled LVDS Outputs

The Si5335 LVDS output can drive an ac-coupled load. The ac coupling capacitors may be placed at either the driver or receiver end, as long as they are placed prior to the  $100\,\Omega$  termination resistor. Keep the  $100\,\Omega$  termination resistor as close to the receiver as possible, as shown in Figure 19. When a 1.8 V output supply voltage is used, the LVDS output of the Si5335 produces a common-mode voltage of ~0.875 V, which does not support the LVDS standard. In this case, it is best to ac-couple the output to the load.

Figure 19. Interfacing to an LVDS Receiver

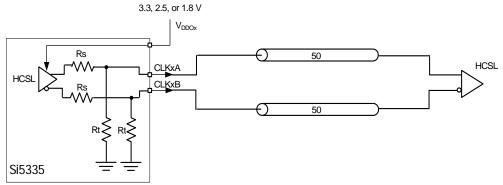

#### 3.10.5. HCSL Outputs

Host clock signal level (HCSL) outputs are commonly used in PCI Express applications. A typical HCSL driver has an open source output that requires an external series resistor and a resistor to ground. The Si5335 HCSL driver has integrated these resistors to simplify the interface to an HCSL receiver. No external components are necessary when connecting the Si5335 HCSL driver to an HCSL receiver.

Figure 20. Interfacing the Si5335 to an HCSL Receiver

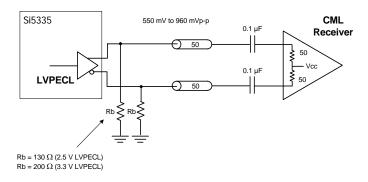

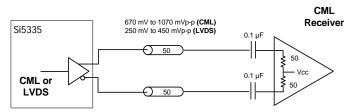

#### 3.10.6. CML Outputs

Current mode logic (CML) is transmitted differentially and terminated to  $50~\Omega$  to Vcc as shown in Figure 20. A CML receiver can be driven with either an LVPECL, CML, or LVDS output. To drive a CML receiver, an Si5335 output configured in LVPECL or CML mode generates a single-ended output swing of 550~mV to 960~mV. However, to reduce power consumption by approximately 15~mA per output driver pair (compared to an LVPECL-configured output), the Si5335's CML output mode can be selected without affecting the output voltage swing. For even lower power consumption, depending on the input signal swing required, CML receivers can be driven with an Si5335 output configured in LVDS mode. CML output format is not available when the Si5335 is in PLL bypass (clock buffer) mode.

#### **Driving a CML Receiver Using the LVPECL Output**

#### Driving a CML Receiver Using the CML or LVDS Output

Figure 21. Terminating an LVPECL or an LVDS Output to a CML Receiver

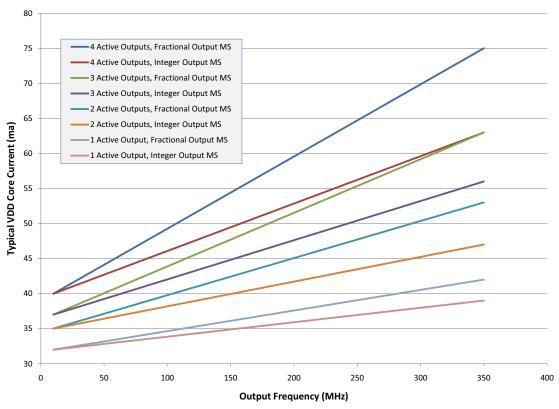

## 4. Power Consumption

In clock generator mode, the Si5335 Power consumption is a function of the following:

- Supply voltage

- Frequency of output Clocks

- Number of output Clocks

- Format of output Clocks

Because of internal voltage regulation, the current from the core  $V_{DD}$  is independent of the  $V_{DD}$  voltage and hence the plot shown in Figure 5 can be used to estimate the  $V_{DD}$  core (pins 7 and 24) current.

The current from the output supply voltages can be estimated from the values provided in Table 2, "DC Characteristics," on page 4. To get the most accurate value for  $V_{DD}$  currents, the Si5338-EVB with ClockBuilder Desktop software should be used.

To do this, go to the "Power" tab of ClockBuilder Desktop and press "Measure". In this manner, a specific configuration can be implemented on the EVB and the actual current for each supply voltage measured. When doing this it is critical that the output drivers have the proper load impedance for the selected format.

When testing for output driver current with HSTL and SSTL, it is required to have load circuitry as shown in "3.10.2. SSTL and HSTL Outputs" on page 27. The Si5338 EVB has layout pads that can be used for this purpose. When testing for output driver current with LVPECL the same layout pads can be used to implement the LVPECL bias resistor of 130  $\Omega$  (2.5 V VDDx) or 200  $\Omega$  (3.3 V VDDx). See the schematic in the Si5338-EVB data sheet and AN408 for additional information.

Figure 22. Core VDD Supply Average Current vs Output Frequency

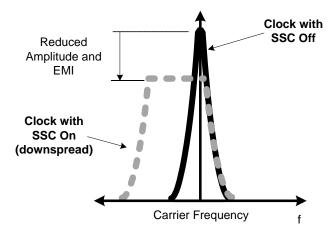

## 5. Spread Spectrum

To help reduce electromagnetic interference (EMI), the Si5335 supports spread spectrum modulation in clock generator mode only. The output clock frequencies can be modulated to spread energy across a broader range of frequencies, lowering system EMI. Spread spectrum modulation is generated digitally in the output MultiSynth dividers, which means that the spread spectrum parameters are virtually independent of process, voltage, and temperature variations.

If the SSENB function is assigned to a pin in ClockBuilder and asserted (driven low), PCIe-compliant spread spectrum is applied to all 100 MHz output clocks with a default spreading rate of 31.5 kHz and 0.5% down spread. If no 100 MHz output clocks are defined but the SSENB is assigned and asserted, none of the output clocks will have spread spectrum clocking applied. Some custom spread-spectrum clocking profiles are available. If the Si5335's default PCIe spread spectrum profile is not suitable for your application, submit your custom spread spectrum requirements for review by visiting the Silicon Labs Technical Support web page at <a href="https://www.silabs.com/support/pages/contacttechnicalsupport.aspx">https://www.silabs.com/support/pages/contacttechnicalsupport.aspx</a>, or contact your local Silicon Labs sales representative for more information.