Home > Products > Intellectual Property > Lattice IP Cores > Gigabit Ethernet PCS

# **Gigabit Ethernet PCS**

\*\*\* A NEW VERSION of this IP core is available. PLEASE VISIT SGMII and Gigabit Ethernet PCS \*\*\*

# **Overview**

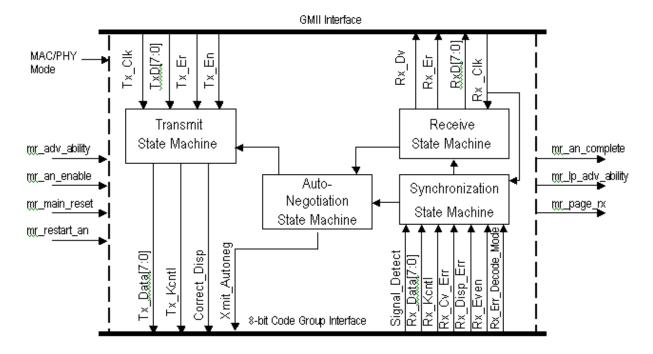

The Gigabit Ethernet (GbE) PCS IP core converts GMII data frames into 8-bit code groups in both transmit and receive directions; and performs auto negotiation with a link partner as described in the IEEE 802.3z specification. The core's block diagram is shown below.

The 1000BASE-X physical layer, also referred to as the GbE physical layer, consists of three major blocks, the Physical Coding Sublayer (PCS), the Physical Medium Attachment sublayer (PMA), and the Physical Medium Dependent sublayer (PMD). The LatticeECP2M™ embedded SERDES/PCS performs the PMA function, and portions of the PMD and PCS functions, including link serialization/deserialization, code-group alignment, clock tolerance compensation buffering, and 8b10b encoding/decoding. However, the embedded SERDES/PCS does not provide all necessary functions for implementing a complete GbE physical layer solution. That's where the GbE PCS IP core comes in. The IP core provides the additional functions required to fully implement the PCS functions of the GbE physical layer. These additional functions include a transmit state machine, a receive state machine, and autonegotiation.

## **Features**

Implements the transmit, receive, and auto-negotiation functions of the IEEE 802.3z specification

8-bit GMII Interface operating at 125 MHz

8-bit Code-Group Interface operating at 125 MHz

Parallel signal interface for control and status management

The GbE PCS is a user-configurable IP core, which allows the configuration of the IP and generation of a netlist and simulation file for use in designs. Please note that generating a bitstream may be prevented or the bitstream may have time logic present unless a license for the IP is purchased.

#### **Resource Utilization**

# Results for LatticeECP2M/S1

| SLICEs | LUTs | Registers | EBRs |

|--------|------|-----------|------|

| 350    | 447  | 417       | 0    |

<sup>&</sup>lt;sup>1</sup> Utilization characteristics are in Lattice's ispLEVER® v7.1 software. When using this IP core in a different software version, utilization may vary.

# **Ordering Information**

Part Numbers:

For LatticeECP2M/S: GBE-PCS-PM-U1

To download a full evaluation version of this IP, please go to the Lattice IP Server tab in the IPexpress Main Window. All ispLeverCORE IP modules available for download are visible on this tab. To find out how to purchase the Gigabit Ethernet PCS IP Core, please contact your local Lattice Sales Office.