## ST7FLITE0

# 8-BIT MCU WITH SINGLE VOLTAGE FLASH MEMORY, DATA EEPROM, ADC, TIMERS, SPI

**DATA BRIEFING**

#### Memories

- 1.5K bytes single voltage Flash Program memory with read-out protection, In-Circuit Programming and In-Application Programming (ICP and IAP). 10K write/erase cycles guaranteed

- 128 bytes RAM

- 128 bytes data EEPROM with read-out protection. 300K write/erase cycles guaranteed

#### ■ Clock, Reset and Supply Management

- 3-level low voltage supervisor (LVD) and auxiliary voltage detector (AVD) for safe power-on/off procedures

- Clock sources: internal 1MHz RC 1% oscillator or external clock

- Optional PLL x4 or x8 for 4 or 8 MHz internal clock

- Four Power Saving Modes: Halt, Active-Halt, Wait and Slow

## ■ Interrupt Management

- 10 interrupt vectors plus TRAP and RESET

- 4 external interrupt lines (on 4 vectors)

## ■ I/O Ports

- 13 multifunctional bidirectional I/O lines

- 9 alternate function lines

- 6 high sink outputs

#### ■ 2 Timers

- One 8-bit Lite Timer with prescaler including: watchdog, 1 realtime base and 1 input capture.

- One 12-bit Auto-reload Timer with output compare function and PWM

#### ■ 1 Communication Interface

SPI synchronous serial interface

#### A/D Converter

- 8-bit resolution for 0 to V<sub>DD</sub>

- Fixed gain Op-amp for 11-bit resolution in 0 to 250 mV range (@ 5V V<sub>DD</sub>)

- 5 input channels

#### ■ Instruction Set

- 8-bit data manipulation

- 63 basic instructions

- 17 main addressing modes

- 8 x 8 unsigned multiply instruction

- True bit manipulation

#### Development Tools

- Full hardware/software development package

#### **Device Summary**

| Features               | ST7FLite09                                                                  | ST7FLite05       |  |  |  |  |

|------------------------|-----------------------------------------------------------------------------|------------------|--|--|--|--|

| Program memory - bytes | 1.5K Flash                                                                  | 1.5K Flash       |  |  |  |  |

| RAM (stack) - bytes    | 128 (64)                                                                    | 128 (64)         |  |  |  |  |

| Data EEPROM - bytes    | 128                                                                         | -                |  |  |  |  |

| Peripherals            | Lite Timer w/ Watchdog, Autoreload Timer w/ 1 PWM, SPI, 8-bit ADC w/ Op-Amp |                  |  |  |  |  |

| Operating Supply       | 2.4V to 5.5V                                                                |                  |  |  |  |  |

| CPU Frequency          | 1MHz RC 1% + PLLx4/8MHz                                                     |                  |  |  |  |  |

| Operating Temperature  | -40°C to +85°C                                                              |                  |  |  |  |  |

| Packages               | SO16 150", DIP16                                                            | SO16 150", DIP16 |  |  |  |  |

Rev. 2.1

## 1 INTRODUCTION

The ST7FLITE0 is a member of the ST7 microcontroller family. All ST7 devices are based on a common industry-standard 8-bit core, featuring an enhanced instruction set.

The ST7FLITE0 features FLASH memory with byte-by-byte In-Circuit Programming (ICP) and In-Application Programming (IAP) capability.

Under software control, the ST7FLITE0 device can be placed in WAIT, SLOW, or HALT mode, reducing power consumption when the application is in idle or standby state.

The enhanced instruction set and addressing modes of the ST7 offer both power and flexibility to software developers, enabling the design of highly efficient and compact application code. In addition to standard 8-bit data management, all ST7 microcontrollers feature true bit manipulation, 8x8 unsigned multiplication and indirect addressing modes.

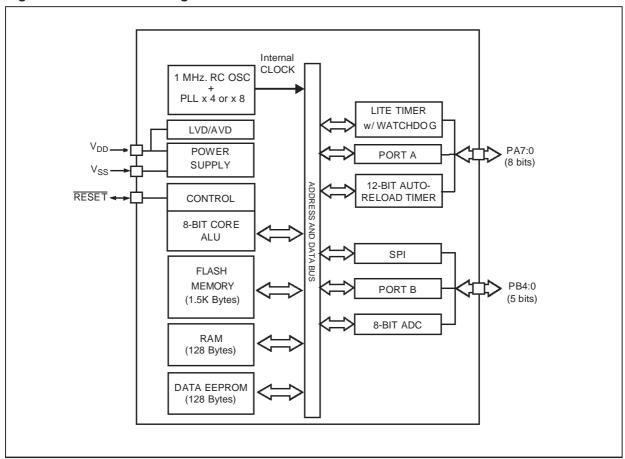

Figure 1. General Block Diagram

57

## **2 PIN DESCRIPTION**

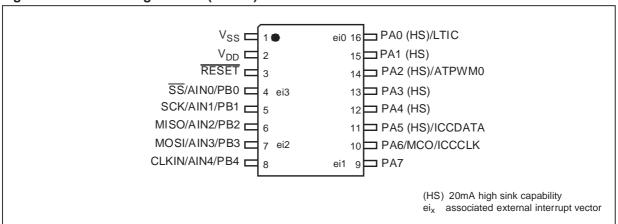

Figure 2. 16-Pin Package Pinout (150mil)

#### ST7FLITE0

## PIN DESCRIPTION (Cont'd)

#### Legend / Abbreviations for Table 1:

Type: I = input, O = output, S = supply

In/Output level: C= CMOS 0.15V<sub>DD</sub>/0.85V<sub>DD</sub> with input trigger

$C_T = CMOS \ 0.3V_{DD}/0.7V_{DD}$  with input trigger

Output level: HS = 20mA high sink (on N-buffer only)

Port and control configuration:

Input: float = floating, wpu = weak pull-up, int = interrupt <sup>1)</sup>, ana = analog

- Output: OD = open drain  $^{2)}$ , PP = push-pull

The RESET configuration of each pin is shown in bold which is valid as long as the device is in reset state.

**Table 1. Device Pin Description**

| Pin<br>n° | Pin Name        | Type | Level Port / Contr |                | rol   |     | BA a i u |        |    |                  |                    |                                                         |

|-----------|-----------------|------|--------------------|----------------|-------|-----|----------|--------|----|------------------|--------------------|---------------------------------------------------------|

|           |                 |      | Input              | Output         | Input |     |          | Output |    | Main<br>Function | Alternate Function |                                                         |

| "         |                 |      |                    |                | float | mdw | int      | ana    | OO | РР               | (after reset)      |                                                         |

| 1         | V <sub>SS</sub> | S    |                    |                |       |     |          |        |    |                  | Ground             |                                                         |

| 2         | $V_{DD}$        | S    |                    |                |       |     |          |        |    |                  | Main power         | supply                                                  |

| 3         | RESET           | I/O  | C <sub>T</sub>     |                |       | Х   |          |        | Х  |                  | Top priority r     | non maskable interrupt (active low)                     |

| 4         | PB0/AIN0/SS     | I/O  | C <sub>T</sub>     |                | Х     | ei  | i3       |        | Х  | Х                | Port B0            | ADC Analog Input 0 or SPI Slave Select (active low)     |

| 5         | PB1/AIN1/SCK    | I/O  | C <sub>T</sub>     |                | Х     | Х   |          |        | Х  | Х                | Port B1            | ADC Analog Input 1 or SPI Serial Clock                  |

| 6         | PB2/AIN2/MISO   | I/O  | C                  | C <sub>T</sub> |       | Х   |          |        | Х  | Х                | Port B2            | ADC Analog Input 2 or SPI Master In/ Slave Out Data     |

| 7         | PB3/AIN3/MOSI   | I/O  | C <sub>T</sub>     |                | Х     | ei  | i2       |        | Х  | Х                | Port B3            | ADC Analog Input 3 or SPI Master<br>Out / Slave In Data |

| 8         | PB4/AIN4/CLKIN  | I/O  | C                  | C <sub>T</sub> |       | Х   |          |        | Х  | Х                | Port B4            | ADC Analog Input 4 or External clock input              |

| 9         | PA7             | 1/0  | СТ                 |                | Х     | ei  | i1       |        | Х  | Х                | Port A7            |                                                         |

| 10        | PA6 /MCO/ICCCLK | I/O  | C <sub>T</sub>     |                | Х     | Х   |          |        | Х  | Х                | Port A6            | Main Clock Output/In Circuit Communication Clock        |

| 11        | PA5/<br>ICCDATA | I/O  | C <sub>T</sub>     | HS             | Х     | Х   |          |        | Х  | Х                | Port A5            | In Circuit Communication Data                           |

| 12        | PA4             | I/O  | $C_{T}$            | HS             | Х     | Х   |          |        | Х  | Х                | Port A4            |                                                         |

| 13        | PA3             | I/O  | C <sub>T</sub>     | HS             | Х     | Х   |          |        | Х  | Х                | Port A3            |                                                         |

| 14        | PA2/ATPWM0      | I/O  | СТ                 | HS             | Х     | Х   |          |        | Х  | Х                | Port A2            | Auto-Reload Timer PWM0                                  |

| 15        | PA1             | I/O  | СТ                 | HS             | Х     | Х   |          |        | Х  | Х                | Port A1            |                                                         |

| 16        | PA0/LTIC        | I/O  | $C_{T}$            | HS             | Х     | ei  | i0       |        | Х  | Х                | Port A0            | Lite Timer Input Capture                                |

#### Note:

4/6

In the interrupt input column, " $ei_x$ " defines the associated external interrupt vector. If the weak pull-up column (wpu) is merged with the interrupt column (int), then the I/O configuration is pull-up interrupt input, else the configuration is floating interrupt input.

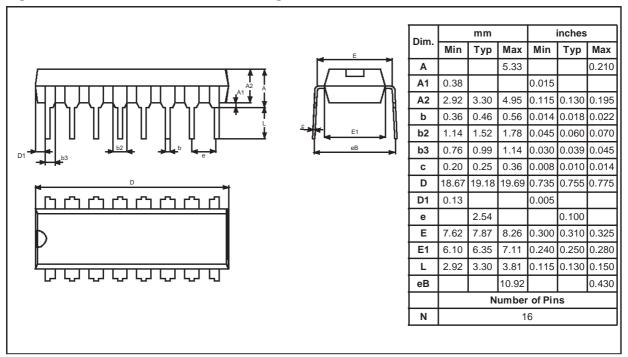

## **3 PACKAGE CHARACTERISTICS**

## 3.1 PACKAGE MECHANICAL DATA

Figure 3. 16-Pin Plastic Dual In-Line Package, 300-mil Width

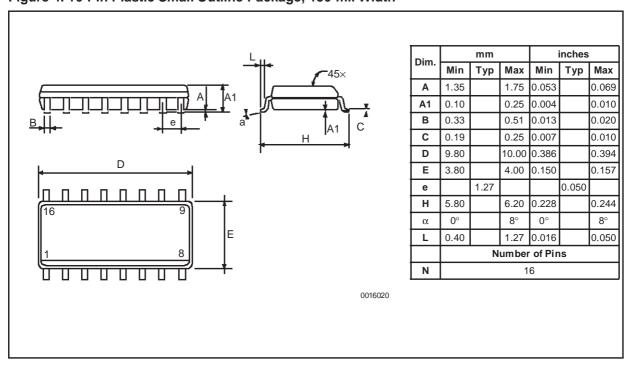

Figure 4. 16-Pin Plastic Small Outline Package, 150-mil Width

| NI | otes: |  |

|----|-------|--|

| N  | ULDE. |  |

|    | olos. |  |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without the express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

©2002 STMicroelectronics - All Rights Reserved.

Purchase of I<sup>2</sup>C Components by STMicroelectronics conveys a license under the Philips I<sup>2</sup>C Patent. Rights to use these components in an I<sup>2</sup>C system is granted provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

STMicroelectronics Group of Companies

Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A. <a href="http://www.st.com">http://www.st.com</a>