#### Is Now Part of

# ON Semiconductor®

To learn more about ON Semiconductor, please visit our website at <a href="https://www.onsemi.com">www.onsemi.com</a>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, emplo

# FAN4860 3 MHz, Synchronous TinyBoost™ Regulator

#### **Features**

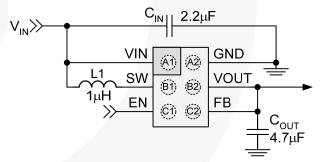

- Operates with Few External Components: 1 μH Inductor and 0402 Case Size Input and Output Capacitors

- Input Voltage Range from 2.3 V to 5.4 V

- Fixed 3.3 V, 5.0 V, or 5.4 V Output Voltage Options

- Maximum Load Current >150 mA at V<sub>IN</sub>=2.3 V

- Maximum Load Current 300 mA at V<sub>IN</sub>=3.3 V, V<sub>OUT</sub>=5.4 V

- Maximum Load Current 300 mA at V<sub>IN</sub>=3.3 V, V<sub>OUT</sub>=5.0 V

- Maximum Load Current 300 mA at V<sub>IN</sub>=2.7 V, V<sub>OUT</sub>=3.3 V

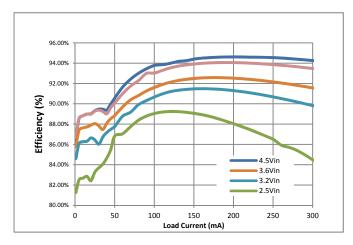

- Up to 92% Efficient

- Low Operating Quiescent Current

- True Load Disconnect During Shutdown

- Variable On-time Pulse Frequency Modulation (PFM) with Light-Load Power-Saving Mode

- Internal Synchronous Rectifier (No External Diode Needed)

- Thermal Shutdown and Overload Protection

- 6-Pin 2 x 2 mm UMLP

- 6-Bump WLCSP, 0.4 mm Pitch

## **Applications**

- USB "On the Go" 5 V Supply

- 5 V Supply HDMI, H-Bridge Motor Drivers

- Powering 3.3 V Core Rails

- PDAs, Portable Media Players

- Cell Phones, Smart Phones, Portable Instruments

## Description

The FAN4860 is a low-power boost regulator designed to provide a regulated 3.3 V, 5.0 V or 5.4 V output from a single cell Lithium or Li-lon battery. Output voltage options are fixed at 3.3 V, 5.0 V, or 5.4 V with a guaranteed maximum load current of 200 mA at  $V_{\rm IN}{=}2.3$  V and 300 mA at  $V_{\rm IN}{=}3.3$  V. Input current in Shutdown Mode is less than 1  $\mu A$ , which maximizes battery life.

Light-load PFM operation is automatic and "glitch-free". The regulator maintains output regulation at no-load with as low as  $37 \mu A$  quiescent current.

The combination of built-in power transistors, synchronous rectification, and low supply current make the FAN4860 ideal for battery powered applications.

The FAN4860 is available in 6-bump 0.4 mm pitch Wafer-Level Chip Scale Package (WLCSP) and a 6-lead 2x2 mm ultra-thin MLP package.

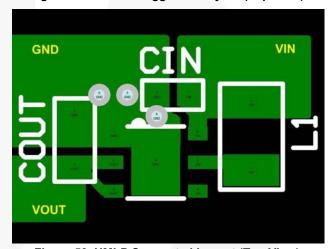

Figure 1. Typical Application

## **Ordering Information**

| Part Number  | Operating Temperature Range | Package             | Packing Method |

|--------------|-----------------------------|---------------------|----------------|

| FAN4860UC5X  | -40°C to 85°C               | WLCSP, 0.4 mm Pitch | Tape and Reel  |

| FAN4860UMP5X | -40°C to 85°C               | UMLP-6, 2 x 2 mm    | Tape and Reel  |

| FAN4860UC33X | -40°C to 85°C               | WLCSP, 0.4 mm Pitch | Tape and Reel  |

| FAN4860UC54X | -40°C to 85°C               | WLCSP, 0.4 mm Pitch | Tape and Reel  |

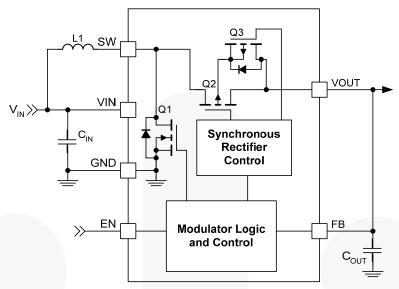

## **Block Diagrams**

Figure 2. IC Block Diagram

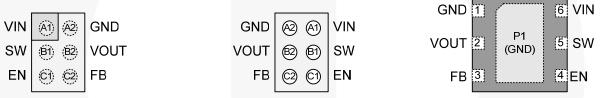

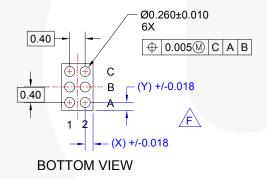

## **Pin Configurations**

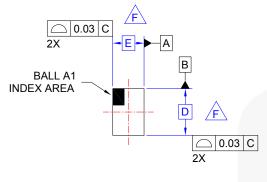

Figure 3. WLCSP (Top View)

Figure 4. WLCSP (Bottom View)

Figure 5. 2x2 mm UMLP (Top View)

## **Pin Definitions**

| Pin   | #     | Name | Description                                                                                                       |  |  |

|-------|-------|------|-------------------------------------------------------------------------------------------------------------------|--|--|

| WLCSP | UMLP  | Name | Description                                                                                                       |  |  |

| A1    | 6     | VIN  | Input Voltage. Connect to Li-Ion battery input power source and input capacitor $(C_{IN})$ .                      |  |  |

| B1    | 5     | SW   | Switching Node. Connect to inductor.                                                                              |  |  |

| C1    | 4     | EN   | <b>Enable</b> . When this pin is HIGH, the circuit is enabled. This pin should not be left floating.              |  |  |

| C2    | 3     | FB   | <b>Feedback</b> . Output voltage sense point for $V_{OUT}$ . Connect to output capacitor ( $C_{OUT}$ ).           |  |  |

| B2    | 2     | VOUT | Output Voltage. This pin is both the output voltage terminal as well as an IC bias supply.                        |  |  |

| A2    | 1, P1 | GND  | <b>Ground</b> . Power and signal ground reference for the IC. All voltages are measured with respect to this pin. |  |  |

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           |                                | Parameter                            |                 |      | Units |

|------------------|--------------------------------|--------------------------------------|-----------------|------|-------|

| V <sub>IN</sub>  | VIN Pin                        |                                      | -0.3            | 5.5  | V     |

| V <sub>OUT</sub> | VOUT Pin                       |                                      | -2              | 6    | V     |

| V <sub>FB</sub>  | FB Pin                         |                                      | -2              | 6    | V     |

| W                | SW Node                        | DC                                   | -0.3            | 5.5  | V     |

| $V_{\sf SW}$     | 3W Node                        | Transient: 10 ns, 3 MHz              | -1.0            | 6.5  |       |

| $V_{EN}$         | EN Pin                         |                                      | -0.3            | 5.5  | V     |

| ESD              | Electrostatic Discharge        | Human Body Model per JESD22-A114     | 2               |      | kV    |

| ESD              | Protection Level               | Charged Device Model per JESD22-C101 |                 | 1    | , KV  |

| T <sub>J</sub>   | Junction Temperature           |                                      | <del>-4</del> 0 | +150 | °C    |

| T <sub>STG</sub> | Storage Temperature            |                                      | <b>–</b> 65     | +150 | °C    |

| T∟               | Lead Soldering Temperature, 10 | Seconds                              |                 | +260 | °C    |

## **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to absolute maximum ratings.

| Symbol           | Parameter                                                |                      | Min. | Max. | Units |

|------------------|----------------------------------------------------------|----------------------|------|------|-------|

|                  | 5.4 V <sub>OUT</sub>                                     |                      | 2.3  | 4.5  |       |

| $V_{IN}$         | Supply Voltage 5.0 V <sub>OUT</sub> 3.3 V <sub>OUT</sub> | 5.0 V <sub>OUT</sub> | 2.3  | 4.5  | V     |

|                  |                                                          | 3.3 V <sub>OUT</sub> | 2.3  | 3.2  |       |

| I <sub>OUT</sub> | Output Current                                           | Output Current       |      | 200  | mA    |

| T <sub>A</sub>   | Ambient Temperature                                      |                      | -40  | +85  | °C    |

| TJ               | Junction Temperature                                     |                      | -40  | +125 | °C    |

## **Thermal Properties**

Junction-to-ambient thermal resistance is a function of application and board layout. This data is measured with four-layer 2s2p boards in accordance to JEDEC standard JESD51. Special attention must be paid not to exceed junction temperature  $T_{J(max)}$  at a given ambient temperate  $T_A$ .

| S | ymbol           | Parameter                              |       | Typical | Units |

|---|-----------------|----------------------------------------|-------|---------|-------|

|   | $\theta_{JA}$ . | Junction-to-Ambient Thermal Resistance | WLCSP | 130     | °C/W  |

|   |                 |                                        | UMLP  | 57      | °C/W  |

## **Electrical Specifications**

Minimum and maximum values are at  $V_{IN}=V_{EN}=2.3~V$  to 4.5 V (2.5 to 3.2  $V_{IN}$  for 3.3  $V_{OUT}$  option),  $T_A=-40^{\circ}C$  to +85°C; circuit of Figure 1, unless otherwise noted. Typical values are at  $T_A=25^{\circ}C$ ,  $V_{IN}=V_{EN}=3.6~V$  for  $V_{OUT}=5.0~V$  / 5.4 V, and  $V_{IN}=V_{EN}=2.7~V$  for  $V_{OUT}=3.3~V$ .

| Symbol               | Param                                       | eter                 | Conditions                                                                 | Min.           | Тур.           | Max.           | Units       |  |

|----------------------|---------------------------------------------|----------------------|----------------------------------------------------------------------------|----------------|----------------|----------------|-------------|--|

|                      |                                             |                      | Quiescent: V <sub>IN</sub> =3.6 V, I <sub>OUT</sub> =0, EN=V <sub>IN</sub> |                | 37             | 45             |             |  |

|                      |                                             | 5.4 V <sub>OUT</sub> | Shutdown: EN=0, V <sub>IN</sub> =3.6 V                                     |                | 0.5            | 1.5            | 1           |  |

|                      |                                             | 501/                 | Quiescent: V <sub>IN</sub> =3.6 V, I <sub>OUT</sub> =0, EN=V <sub>IN</sub> |                | 37             | 45             | ┦           |  |

| I <sub>IN</sub>      | V <sub>IN</sub> Input Current               | 5.0 V <sub>OUT</sub> | Shutdown: EN=0, V <sub>IN</sub> =3.6 V                                     |                | 0.5            | 1.5            | μΑ          |  |

|                      |                                             |                      | Quiescent: V <sub>IN</sub> =2.7 V, I <sub>OUT</sub> =0, EN=V <sub>IN</sub> |                | 50             | 65             |             |  |

|                      |                                             | 3.3 V <sub>OUT</sub> | Shutdown: EN=0, V <sub>IN</sub> =2.7 V                                     |                | 0.5            | 1.5            |             |  |

| I <sub>LK_OUT</sub>  | V <sub>OUT</sub> Leakage Curre              | ent                  | V <sub>OUT</sub> =0, EN=0, V <sub>IN</sub> ≥3 V                            |                | 10             |                | nA          |  |

|                      |                                             |                      | V <sub>OUT</sub> =5.4 V, V <sub>IN</sub> =3.6 V, EN=0                      |                |                |                |             |  |

| I <sub>LK RVSR</sub> | V <sub>OUT</sub> to V <sub>IN</sub> Reverse | e Leakage            | V <sub>OUT</sub> =5.0 V, V <sub>IN</sub> =3.6 V, EN=0                      |                |                | 2.5            | μА          |  |

| _                    |                                             |                      | V <sub>OUT</sub> =3.3 V, V <sub>IN</sub> =3.0 V, EN=0                      |                |                |                |             |  |

| V <sub>UVLO</sub>    | Under-Voltage Lock                          | cout                 | V <sub>IN</sub> Rising                                                     |                | 2.2            | 2.3            | V           |  |

| V <sub>UVLO_HY</sub> | Under-Voltage Lock                          | cout Hysteresis      |                                                                            |                | 190            |                | mV          |  |

| V <sub>ENH</sub>     | Enable HIGH Volta                           |                      |                                                                            | 1.05           |                |                | V           |  |

| VENL                 | Enable LOW Voltage                          | -                    |                                                                            | 1.00           |                | 0.4            | V           |  |

|                      | Enable Input Leaka                          |                      |                                                                            | $\rightarrow$  | 0.01           | 1.00           | μА          |  |

| I <sub>LK_EN</sub>   | Lilabic Iliput Leaka                        | ge Guirent           | V <sub>IN</sub> from 2.3 V to 4.5 V, I <sub>OUT</sub> ≤200 mA              | 5.15           | 5.40           | 5.50           | μΑ          |  |

| $V_{OUT}$            | Output Voltage<br>Accuracy <sup>(1)</sup>   | 5.4 V <sub>OUT</sub> | V <sub>IN</sub> from 2.7 V to 4.5 V, I <sub>OUT</sub> ≤200 mA              | 5.20           | 5.40           | 5.50           |             |  |

|                      |                                             | 3.4 0001             | V <sub>IN</sub> from 3.3 V to 4.5 V, I <sub>OUT</sub> ≤300 mA              | 5.15           | 5.40           | 5.50           |             |  |

|                      |                                             |                      | V <sub>IN</sub> from 2.3 V to 4.5 V, I <sub>OUT</sub> ≤200 mA              | 4.80           | 5.05           | 5.15           | V           |  |

|                      |                                             | 5.0 V <sub>OUT</sub> | V <sub>IN</sub> from 2.7 V to 4.5 V, I <sub>OUT</sub> ≤200 mA              | 4.85           | 5.05           | 5.15           | -<br>-<br>- |  |

|                      |                                             | 3.0 VOUT             | V <sub>IN</sub> from 3.3 V to 4.5 V, I <sub>OUT</sub> ≤300 mA              | 4.85           | 5.05           | 5.15           |             |  |

|                      |                                             | 3.3 V <sub>OUT</sub> | V <sub>IN</sub> from 2.5 V to 3.2 V, I <sub>OUT</sub> ≤200 mA              | 3.17           | 3.33           | 3.41           |             |  |

|                      |                                             | 3.3 V <sub>OUT</sub> | Referred to V <sub>OUT</sub> =5.4 V                                        |                |                |                |             |  |

| \/                   | Defended Assument                           |                      |                                                                            | 5.325<br>4.975 | 5.400<br>5.050 | 5.475<br>5.125 | ┤ ,, │      |  |

| $V_{REF}$            | Reference Accurac                           | у                    | Referred to V <sub>OUT</sub> =5.0 V<br>Referred to V <sub>OUT</sub> =3.3 V | 3.280          | 3.330          | 3.380          | _ V         |  |

| $\rightarrow$        |                                             |                      | V <sub>IN</sub> =3.6 V, V <sub>OUT</sub> =5.4 V, I <sub>OUT</sub> =200 mA  | 185            | 230            | 255            | +           |  |

|                      | Off Time                                    |                      |                                                                            | 195            | 240            | 265            |             |  |

| t <sub>OFF</sub>     | Oli Tillie                                  |                      | V <sub>IN</sub> =3.6 V, V <sub>OUT</sub> =5.0 V, I <sub>OUT</sub> =200 mA  |                |                |                | ns          |  |

|                      |                                             |                      | V <sub>IN</sub> =2.7 V, V <sub>OUT</sub> =3.3 V, I <sub>OUT</sub> =200 mA  | 240            | 290            | 350            |             |  |

|                      |                                             | 5.4.1/               | V <sub>IN</sub> =2.3 V                                                     | 200            |                |                |             |  |

|                      |                                             | 5.4 V <sub>OUT</sub> | V <sub>IN</sub> =3.3 V                                                     | 300            | 400            |                |             |  |

|                      |                                             |                      | V <sub>IN</sub> =3.6 V<br>V <sub>IN</sub> =2.3 V                           | 200            | 400            |                | 1           |  |

| $I_{OUT}$            | Maximum Output<br>Current <sup>(1)</sup>    | 5.0 V <sub>OUT</sub> | V <sub>IN</sub> =3.3 V                                                     | 300            |                | H              | mA          |  |

|                      | Carrent                                     | 5.0 VOUT             | V <sub>IN</sub> =3.6 V                                                     | 300            | 400            |                |             |  |

|                      |                                             |                      |                                                                            | 250            | 400            |                |             |  |

|                      |                                             | $3.3 V_{OUT}$        | V <sub>IN</sub> =2.5 V<br>V <sub>IN</sub> =2.7 V                           | 250            |                | -              | ┥ !         |  |

|                      |                                             | 5.4.1/               |                                                                            | 300            | 1400           | 1500           | 1           |  |

|                      | SW Peak Current                             | 5.4 V <sub>OUT</sub> | V <sub>IN</sub> =3.6 V, V <sub>OUT</sub> >V <sub>IN</sub>                  | 1000           | 1400           | 1500           | - m^        |  |

| I <sub>SW</sub>      | Limit                                       | 5.0 V <sub>OUT</sub> | $V_{IN}$ =3.6 V, $V_{OUT}$ > $V_{IN}$                                      | 930            | 1100           | 1320           | mA          |  |

|                      |                                             | 3.3 V <sub>OUT</sub> | V <sub>IN</sub> =2.7 V, V <sub>OUT</sub> >V <sub>IN</sub>                  | 650            | 800            | 950            |             |  |

Continued on the following page...

## **Electrical Specifications**

Minimum and maximum values are at  $V_{IN}=V_{EN}=2.3~V$  to 4.5 V (2.5 to 3.2  $V_{IN}$  for 3.3  $V_{OUT}$  option),  $T_A=-40^{\circ}C$  to +85°C; circuit of Figure 1, unless otherwise noted. Typical values are at  $T_A=25^{\circ}C$ ,  $V_{IN}=V_{EN}=3.6~V$  for  $V_{OUT}=5.0~V$  / 5.4 V, and  $V_{IN}=V_{EN}=2.7~V$  for  $V_{OUT}=3.3~V$ .

| Symbol               | Paramete                                              | er                   | Conditions                                                 | Min. | Тур. | Max. | Units |

|----------------------|-------------------------------------------------------|----------------------|------------------------------------------------------------|------|------|------|-------|

|                      |                                                       | 5.4 V <sub>OUT</sub> | V <sub>IN</sub> =3.6 V, V <sub>OUT</sub> < V <sub>IN</sub> |      | 900  |      |       |

| I <sub>SS</sub>      | Soft-Start Input Peak<br>Current Limit <sup>(2)</sup> | 5.0 V <sub>OUT</sub> | $V_{IN}$ =3.6 V, $V_{OUT}$ < $V_{IN}$                      |      | 850  |      | mA    |

|                      | Garrent Enric                                         | $3.3\ V_{OUT}$       | $V_{IN}$ =2.7 V, $V_{OUT}$ < $V_{IN}$                      |      | 700  |      |       |

|                      | Soft-Start Time <sup>(3)</sup>                        | 5.4 V <sub>OUT</sub> | V <sub>IN</sub> =3.6 V, I <sub>OUT</sub> =200 mA           |      | 270  | 400  |       |

| tss                  |                                                       | $5.0\ V_{OUT}$       | V <sub>IN</sub> =3.6 V, I <sub>OUT</sub> =200 mA           |      | 100  | 300  | μS    |

|                      |                                                       | $3.3\ V_{OUT}$       | V <sub>IN</sub> =2.7 V, I <sub>OUT</sub> =200 mA           |      | 250  | 750  |       |

| D                    | N-Channel Boost Swit                                  | ch                   | V <sub>IN</sub> =3.6 V                                     |      | 300  |      | mΩ    |

| R <sub>DS(ON)</sub>  | P-Channel Sync Rectifier                              |                      | V <sub>IN</sub> =3.6 V                                     |      | 400  |      | 11122 |

| $T_{TSD}$            | Thermal Shutdown                                      |                      | I <sub>LOAD</sub> =10 mA                                   |      | 150  |      | °C    |

| T <sub>TSD_HYS</sub> | Thermal Shutdown Hy                                   | steresis             |                                                            |      | 30   |      | °C    |

#### **Notes**

- 1.  $I_{LOAD}$  from 0 to  $I_{OUT}$ ; also includes load transient response.  $V_{OUT}$  measured from mid-point of output voltage ripple. Effective capacitance of  $C_{OUT} > 1.5 \,\mu\text{F}$ .

- 2. Guaranteed by design and characterization; not tested in production.

- 3. Elapsed time from rising EN until regulated V<sub>OUT</sub>.

## **5.4 V<sub>OUT</sub> Typical Characteristics**

Unless otherwise specified; circuit per Figure 1, 3.6  $V_{IN}$ , and  $T_A$ =25°C.

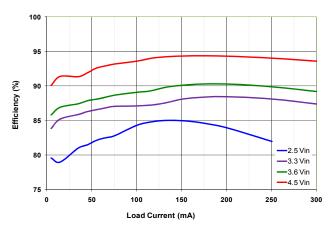

Figure 6. Efficiency vs. V<sub>IN</sub>

rigule o. Efficiency vs. VIN

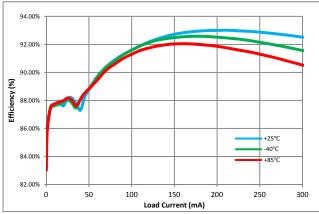

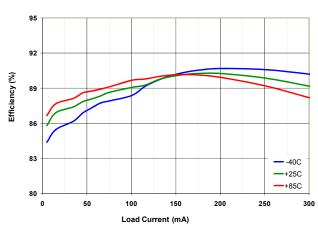

Figure 7. Efficiency vs. Temperature, 3.6 VIN

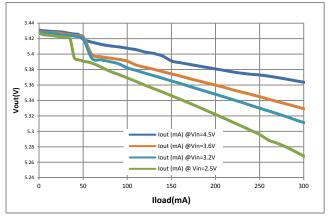

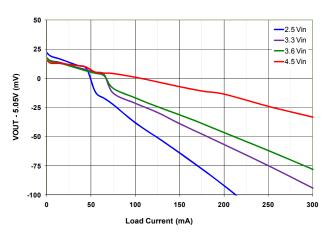

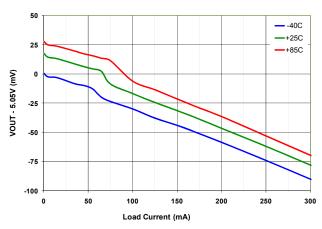

Figure 8. Line and Load Regulation

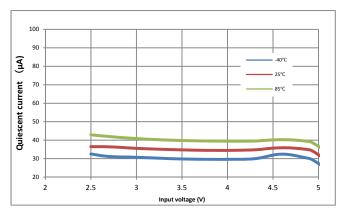

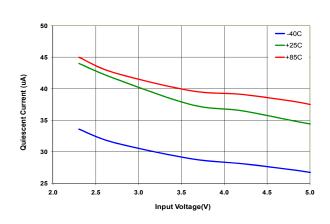

Figure 9. Quiescent Current

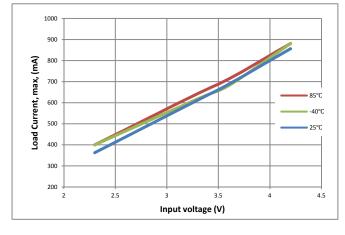

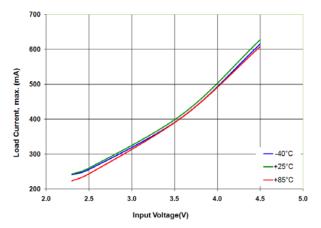

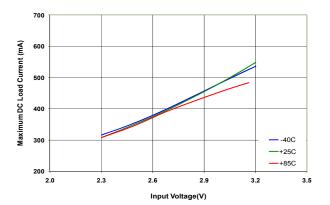

Figure 10. Maximum DC Load Current

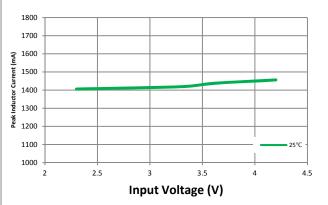

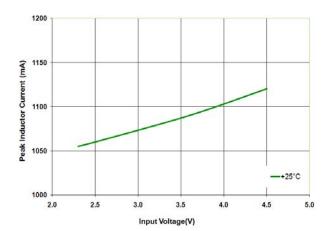

Figure 11. Peak Inductor Current

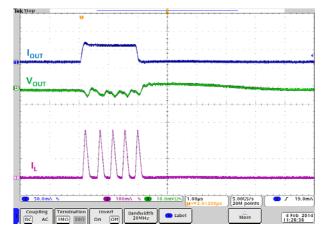

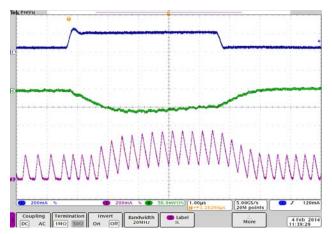

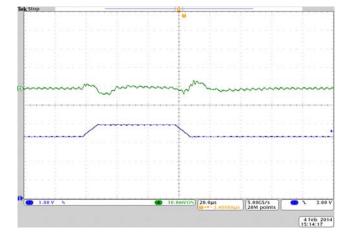

## 5.4 V<sub>OUT</sub> Typical Characteristics

Unless otherwise specified; circuit per Figure 1, 3.6 V<sub>IN</sub>, and T<sub>A</sub>=25°C.

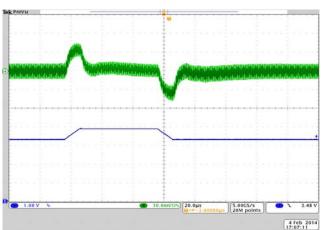

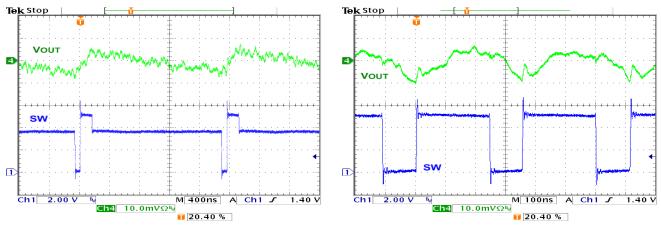

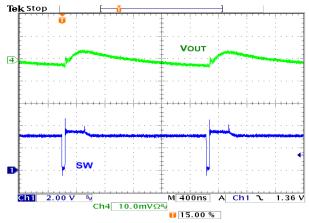

Figure 12. 0-50 mA Load Transient, 100 ns Step

Figure 13. 50-200 mA Load Transient, 100 ns Step

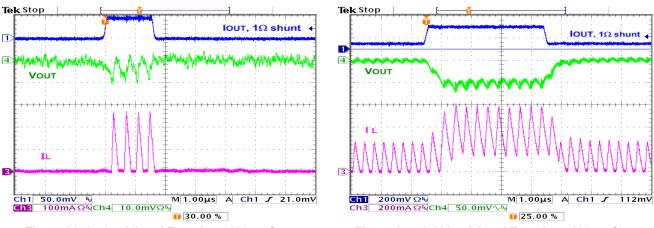

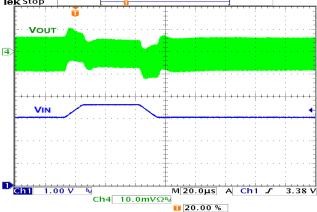

Figure 14. Line Transient, 5 mA Load, 10 µs Step

Figure 15. Line Transient, 200 mA Load, 10 µs Step

## **5.0 V<sub>OUT</sub> Typical Characteristics**

Figure 16. Efficiency vs. V<sub>IN</sub>

Figure 17. Efficiency vs. Temperature, 3.6  $V_{\text{IN}}$

## 5.0 V<sub>OUT</sub> Typical Characteristics

Figure 18. Line and Load Regulation

Figure 19. Load Regulation vs. Temperature, 3.6 V<sub>IN</sub>

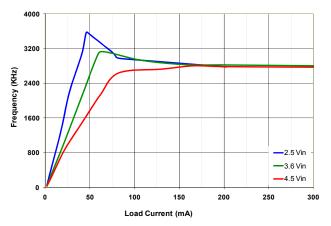

Figure 20. Switching Frequency

Figure 21. Quiescent Current

Figure 22. Maximum DC Load Current

Figure 23. Peak Inductor Current

## 5.0 V<sub>OUT</sub> Typical Characteristics

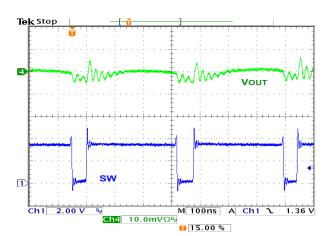

Figure 24. Output Ripple, 10 mA PFM Load

Figure 25. Output Ripple, 200 mA PWM Load

Figure 26. 0-50 mA Load Transient, 100 ns Step

Figure 27. 50-200 mA Load Transient, 100 ns Step

Figure 28. Line Transient, 5 mA Load, 10 µs Step

Figure 29. Line Transient, 200 mA Load, 10 µs Step

## 5.0 V<sub>OUT</sub> Typical Characteristics

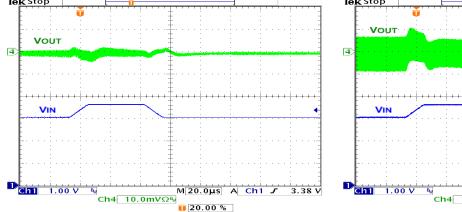

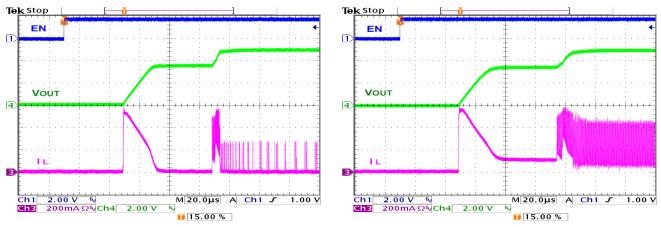

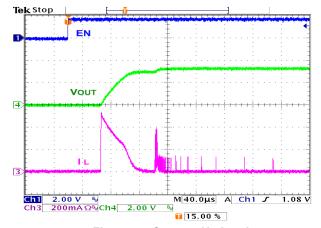

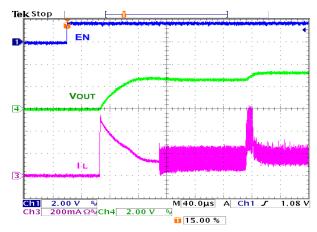

Figure 30. Startup, No Load

Figure 31. Startup, 33 Ω Load

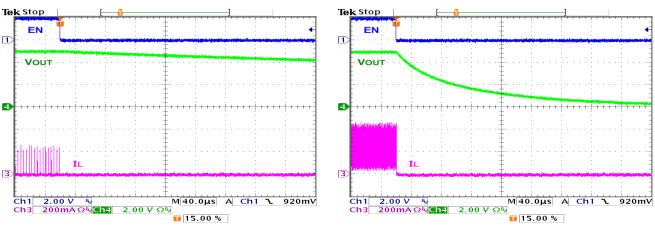

Figure 32. Shutdown, 1  $k\Omega$  Load

Figure 33. Shutdown, 33  $\Omega$  Load

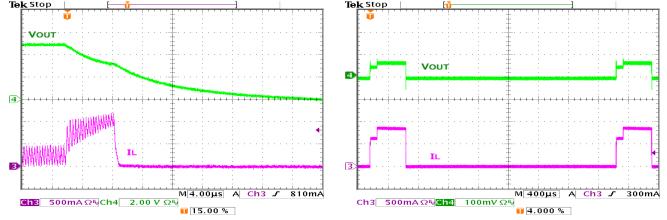

Figure 34. Overload Protection

Figure 35. Short-Circuit Response

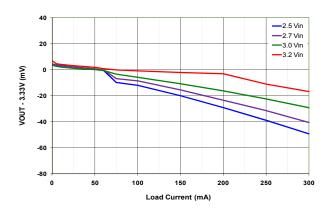

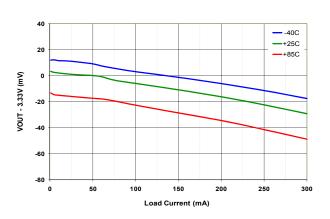

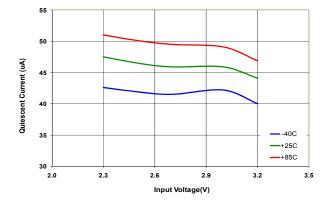

## 3.3 V<sub>OUT</sub> Typical Characteristics

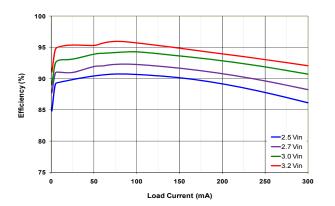

Figure 36. Efficiency vs.  $V_{\text{IN}}$

Figure 37. Efficiency vs. Temperature, 3.0 V<sub>IN</sub>

Figure 38. Line and Load Regulation

Figure 39. Load Regulation vs. Temperature, 3.0 V<sub>IN</sub>

Figure 40. Quiescent Current

Figure 41. Maximum DC Load Current

## 3.3 V<sub>OUT</sub> Typical Characteristics

Figure 42. Output Ripple, 10 mA PFM Load

Figure 43. Output Ripple, 200 mA PWM Load

Figure 44. Startup, No Load

Figure 45. Startup, 22  $\Omega$  Load

## **Functional Description**

#### **Circuit Description**

The FAN4860 is a synchronous boost regulator, typically operating at 3 MHz in Continuous Conduction Mode (CCM), which occurs at moderate to heavy load current and low  $V_{\text{IN}}$  voltages.

At light-load currents, the converter switches automatically to power-saving PFM Mode. The regulator automatically and smoothly transitions between quasi-fixed-frequency continuous conduction PWM Mode and variable-frequency PFM Mode to maintain the highest possible efficiency over the full range of load current and input voltage.

#### **PWM Mode Regulation**

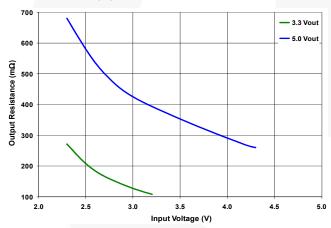

The FAN4860 uses a minimum on-time and computed minimum off-time to regulate  $V_{\text{OUT}}$ . The regulator achieves excellent transient response by employing current mode modulation. This technique causes the regulator output to exhibit a load line. During PWM Mode, the output voltage drops slightly as the input current rises. With a constant  $V_{\text{IN}}$ , this appears as a constant output resistance.

The "droop" caused by the output resistance when a load is applied allows the regulator to respond smoothly to load transients with negligible overshoot.

Figure 46. Output Resistance (ROUT)

When the regulator is in PWM CCM Mode and the target  $V_{\text{OUT}}$  = 5.05 V,  $V_{\text{OUT}}$  is a function of  $I_{\text{LOAD}}$  and can be computed as:

$$V_{OUT} = 5.05 - R_{OUT} \bullet I_{LOAD}$$

(1)

For example, at  $V_{IN}$ =3.3 V, and  $I_{LOAD}$ =200 mA,  $V_{OUT}$  drops to:

$$V_{OUT} = 5.05 - 0.38 \cdot 0.2 = 4.974V$$

(1A)

At V<sub>IN</sub>=2.3 V, and I<sub>LOAD</sub>=200 mA, V<sub>OUT</sub> drops to:

$$V_{OUT} = 5.05 - 0.68 \cdot 0.2 = 4.914V$$

(1B)

#### **PFM Mode**

If  $V_{\text{OUT}} > V_{\text{REF}}$  when the minimum off-time has ended, the regulator enters PFM Mode. Boost pulses are inhibited until  $V_{\text{OUT}} < V_{\text{REF}}$ . The minimum on-time is increased to enable the output to pump up sufficiently with each PFM boost pulse. Therefore, the regulator behaves like a constant on-time regulator, with the bottom of its output voltage ripple at 5.05 V in PFM Mode.

Table 1. Operating States

| Mode | Description          | Invoked When:                      |

|------|----------------------|------------------------------------|

| LIN  | Linear Startup       | $V_{IN} > V_{OUT}$                 |

| SS   | Boost Soft-Start     | $V_{OUT} < V_{REG}$                |

| BST  | Boost Operating Mode | V <sub>OUT</sub> =V <sub>REG</sub> |

#### **Shutdown and Startup**

If EN is LOW, all bias circuits are off and the regulator is in Shutdown Mode. During shutdown, true load disconnect between battery and load prevents current flow from  $V_{\text{IN}}$  to  $V_{\text{OUT}}$ , as well as reverse flow from  $V_{\text{OUT}}$  to  $V_{\text{IN}}$ .

#### LIN State

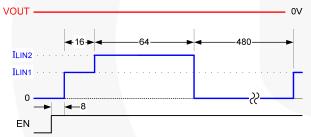

When EN rises, if  $V_{\text{IN}} > \text{UVLO}$ , the regulator first attempts to bring  $V_{\text{OUT}}$  within about 1V of  $V_{\text{IN}}$  by using the internal fixed current source from  $V_{\text{IN}}$  ( $I_{\text{LIN1}}$ ). The current is limited to about 630 mA during LIN1 Mode.

If  $V_{\text{OUT}}$  reaches  $V_{\text{IN}}$ -1V during LIN1 Mode, the SS state is initiated. Otherwise, LIN1 times out after 16 clock counts and the LIN2 Mode is entered.

In LIN2 Mode, the current source is incremented to 850 mA. If  $V_{\text{OUT}}$  fails to reach  $V_{\text{IN}}$ -1 V after 64 clock counts, a fault condition is declared.

#### SS State

Upon the successful completion of the LIN state  $(V_{OUT} \ge V_{IN}-1 V)$ , the regulator begins switching with boost pulses current limited to about 50% of nominal level, incrementing to full scale over a period of 32 clock counts.

If the output fails to achieve 90% of its set point within 96 clock counts at full-scale current limit, a fault condition is declared.

#### **BST State**

This is the normal operating mode of the regulator. The regulator uses a minimum  $t_{\text{OFF}}\text{-minimum}$   $t_{\text{ON}}$  modulation

scheme. Minimum  $t_{OFF}$  is proportional to  $v_{OUT}$ , which keeps the regulator's switching frequency reasonably constant in CCM.  $t_{ON(MIN)}$  is proportional to  $V_{IN}$  and is higher if the inductor current reaches 0 before  $t_{OFF(MIN)}$  during the prior cycle.

To ensure that  $V_{\text{OUT}}$  does not pump significantly above the regulation point, the boost switch remains off as long as FB >  $V_{\text{RFF}}$ .

#### **Fault State**

The regulator enters the FAULT state under any of the following conditions:

- V<sub>OUT</sub> fails to achieve the voltage required to advance from LIN state to SS state.

- V<sub>OUT</sub> fails to achieve the voltage required to advance from SS state to BST state.

- Sustained (32 CLK counts) pulse-by-pulse current limit during the BST state.

- The regulator moves from BST to LIN state due to a short circuit or output overload (V<sub>OUT</sub> < V<sub>IN</sub>-1 V).

Once a fault is triggered, the regulator stops switching and presents a high-impedance path between  $V_{\text{IN}}$  and  $V_{\text{OUT}}$ . After waiting 480 CLK counts, a restart is attempted.

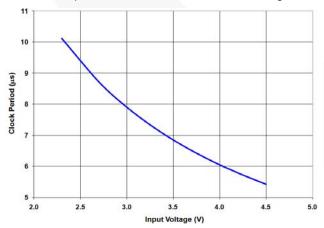

#### **Soft-Start and Fault Timing**

The soft-start timing for each state, and the fault times, are determined by the fault clock, whose period is inversely proportional to  $V_{\text{IN}}$ . This allows the regulator more time to charge larger values of  $C_{\text{OUT}}$  when  $V_{\text{IN}}$  is lower. With higher  $V_{\text{IN}}$ , this also reduces power delivered to  $V_{\text{OUT}}$  during each cycle in current limit.

The number of clock counts for each state is illustrated in Figure 47.

Figure 47. Fault Response into Short Circuit

The fault clock period as a function of V<sub>IN</sub> is shown in Figure 48.

Figure 48. Fault Clock Period vs. VIN

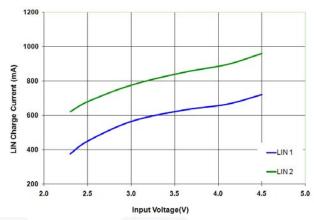

The  $V_{\text{IN}}$ -dependent LIN Mode charging current is illustrated in Figure 49.

Figure 49. LIN Mode Current vs. VIN

## **Over-Temperature Protection (OTP)**

The regulator shuts down when the thermal shutdown threshold is reached. Restart, with soft-start, occurs when the IC has cooled by about 30°C.

#### **Over-Current Protection (OCP)**

During Boost Mode, the FAN4860 employs a cycle-by-cycle peak current limit to protect switching elements. Sustained current limit, for 32 consecutive fault clock counts, initiates a fault condition.

During an overload condition, as  $V_{\text{OUT}}$  collapses to approximately  $V_{\text{IN}}$ -1 V, the synchronous rectifier is immediately switched off and a fault condition is declared.

Automatic restart occurs once the overload/short is removed and the fault timer completes counting.

## **Application Information**

#### **External Component Selection**

Table 2 shows the recommended external components for the FAN4860:

**Table 2. External Components**

| REF              | Description                               | Manufacturer                        |  |  |

|------------------|-------------------------------------------|-------------------------------------|--|--|

| L1               | 1.0 μH, 0.8 A,<br>190 mΩ, 0805            | Murata LQM21PN1R0MC0, or equivalent |  |  |

| C <sub>IN</sub>  | 2.2 μF, 6.3 V, X5R,<br>0402               | Murata GRM155R60J225M               |  |  |

| CIN              |                                           | TDK C1005X5R0J225M                  |  |  |

| C                | 4.7 μF, 10 V, X5R,<br>0603 <sup>(4)</sup> | Kemet C0603C475K8PAC                |  |  |

| C <sub>OUT</sub> | 0603 <sup>(4)</sup>                       | TDK C1608X5R1A475K                  |  |  |

#### Note:

4. A 6.3 V-rated 0603 capacitor may be used for C<sub>OUT</sub>, such as Murata GRM188R60J225M. All datasheet parameters are valid with the 6.3 V-rated capacitor. Due to DC bias effects, the 10 V capacitor offers a performance enhancement; particularly output ripple and transient response, without any size increase.

## Output Capacitance (Cout)

#### Stability

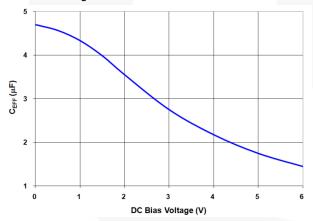

The effective capacitance  $(C_{\text{EFF}})$  of small, high-value, ceramic capacitors decrease as their bias voltage increases, as shown in Figure 50.

Figure 50. C<sub>EFF</sub> for 4.7 μF, 0603, X5R, 6.3 V (Murata GRM188R60J475K)

FAN4860 is guaranteed for stable operation with the minimum value of  $C_{\text{EFF}}$  ( $C_{\text{EFF}(MIN)}$ ) outlined in Table 3.

Table 3. Minimum C<sub>EFF</sub> Required for Stability

| Operating           | C (E)                  |                            |

|---------------------|------------------------|----------------------------|

| V <sub>IN</sub> (V) | I <sub>LOAD</sub> (mA) | C <sub>EFF(MIN)</sub> (μF) |

| 2.3 to 4.5          | 0 to 200               | 1.5                        |

| 2.7 to 4.5          | 0 to 200               | 1.0                        |

| 2.3 to 4.5          | 0 to 150               | 1.0                        |

$C_{\text{EFF}}$  varies with manufacturer, dielectric material, case size, and temperature. Some manufacturers may be able to provide an X5R capacitor in 0402 case size that retains  $C_{\text{EFF}}$  >1.5  $\mu\text{F}$  with 5V bias; others may not. If this  $C_{\text{EFF}}$  cannot be economically obtained and 0402 case size is required, the IC can work with the 0402 capacitor as long as the minimum  $V_{\text{IN}}$  is restricted to >2.7 V.

For best performance, a 10 V-rated 0603 output capacitor is recommended (Kemet C0603C475K8PAC, or equivalent). Since it retains greater C<sub>EFF</sub> under bias and over temperature, output ripple can is reduced and transient capability enhanced.

#### **Output Voltage Ripple**

Output voltage ripple is inversely proportional to  $C_{\text{OUT}}$ . During  $t_{\text{ON}}$ , when the boost switch is on, all load current is supplied by  $C_{\text{OUT}}$ .

$$V_{RIPPLE(P-P)} = t_{ON} \bullet \frac{I_{LOAD}}{C_{OUT}}$$

(2)

and

$$t_{ON} = t_{SW} \bullet D = t_{SW} \bullet \left(1 - \frac{V_{IN}}{V_{OUT}}\right)$$

(3)

Therefore:

$$V_{RIPPLE(P-P)} = t_{SW} \bullet \left(1 - \frac{V_{IN}}{V_{OUT}}\right) \bullet \frac{I_{LOAD}}{C_{OUT}}$$

(4)

where:

$$t_{SW} = \frac{1}{f_{SW}} \tag{5}$$

As can be seen from Equation 4, the maximum  $V_{\text{RIPPLE}}$  occurs when  $V_{\text{IN}}$  is minimum and  $I_{\text{LOAD}}$  is maximum.

#### Startup

Input current limiting is in effect during soft-start, which limits the current available to charge  $C_{\text{OUT}}.$  If the output fails to achieve regulation within the time period described in the soft-start section above; a FAULT occurs, causing the circuit to shut down, then restart after a significant time period. If  $C_{\text{OUT}}$  is a very high value, the circuit may not start on the first attempt, but eventually achieves regulation if no load is present. If a high-current load and high capacitance are both present during soft-start, the circuit may fail to achieve regulation and continually attempt soft-start, only to have  $C_{\text{OUT}}$  discharged by the load when in the FAULT state.

The circuit can start with higher values of  $C_{\text{OUT}}$  under full load if  $V_{\text{IN}}$  is higher, since:

$$I_{OUT} = \left(I_{LIM(PK)} - \frac{I_{RIPPLE}}{2}\right) \bullet \frac{V_{IN}}{V_{OUT}}$$

(6)

Generally, the limitation occurs in BST Mode.

The FAN4860 starts on the first pass (without triggering a FAULT) under the following conditions for C<sub>EFF(MAX)</sub>:

Table 4. Maximum C<sub>EFF</sub> for First-Pass Startup

|                                     | Operating Conditions |                      |                      |                            |  |

|-------------------------------------|----------------------|----------------------|----------------------|----------------------------|--|

| $V_{IN}(V)$ $R_{LOAD(MIN)}(\Omega)$ |                      |                      |                      | C <sub>EFF(MAX)</sub> (μF) |  |

| VIN (V)                             | 5.4 V <sub>OUT</sub> | 5.0 V <sub>OUT</sub> | 3.3 V <sub>OUT</sub> |                            |  |

| > 2.3                               | 27                   | 25                   | 16                   | 10                         |  |

| > 2.7                               | 27                   | 25                   | 16                   | 15                         |  |

| > 2.7                               | 37                   | 33                   | 20                   | 22                         |  |

$C_{\text{EFF}}$  values shown in Table 4 typically apply to the lowest  $V_{\text{IN}}.$  The presence of higher  $V_{\text{IN}}$  enhances ability to start into larger  $C_{\text{EFF}}$  at full load.

#### **Transient Protection**

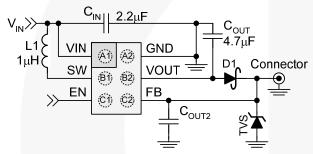

To protect against external voltage transients caused by ESD discharge events, or improper external connections, some applications employ an external transient voltage suppressor (TVS) and Schottky diode (D1 in Figure 51).

Figure 51. FAN4860 with External Transient Protection

The TVS is designed to clamp the FB line (system  $V_{OUT}$ ) to +10 V or -2 V during external transient events. The Schottky diode protects the output devices from the positive excursion. The FB pin can tolerate up to 14 V of positive excursion, while both the FB and VOUT pins can tolerate negative voltages.

The FAN4860 includes a circuit to detect a missing or defective D1 by comparing  $V_{\text{OUT}}$  to FB. If  $V_{\text{OUT}} - \text{FB} > \text{about } 0.7 \text{ V}$ , the IC shuts down. The IC remains shut down until  $V_{\text{OUT}} < \text{UVLO}$  and  $V_{\text{IN}} < \text{UVLO} + 0.7$  or EN is toggled.

$C_{OUT2}$  may be necessary to preserve load transient response when the Schottky is used. When a load is applied at the FB pin, the forward voltage of the D1 rapidly increases before the regulator can respond or the inductor current can change. This causes an immediate drop of up to 300 mV, depending on D1's characteristics if  $C_{OUT2}$  is absent.  $C_{OUT2}$  supplies instantaneous current to the load while the regulator adjusts the inductor current. A value of at least half of the minimum value of  $C_{OUT}$  should be used for  $C_{OUT2}$ .  $C_{OUT2}$  needs to withstand the maximum voltage at the FB pin as the TVS is clamping.

The maximum DC output current available is reduced with this circuit, due to the additional dissipation of D1.

#### **Layout Guideline**

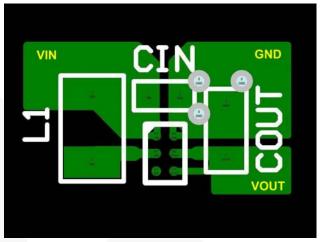

Figure 52. WLCSP Suggested Layout (Top View)

Figure 53. UMLP Suggested Layout (Top View)

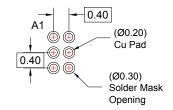

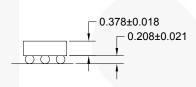

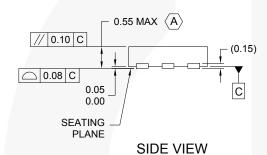

## **Physical Dimensions**

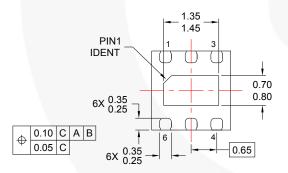

#### **TOP VIEW**

# RECOMMENDED LAND PATTERN (NSMD PAD TYPE)

SIDE VIEWS

#### NOTES:

- A. NO JEDEC REGISTRATION APPLIES.

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCES PER ASMEY14.5M, 1994.

- DATUM C, THE SEATING PLANE IS DEFINED BY THE SPHERICAL CROWNS OF THE BALLS.

- E. PACKAGE TYPICAL HEIGHT IS 586 MICRONS ±39 MICRONS (547-625 MICRONS).

- F. FOR DIMENSIONS D, E, X, AND Y SEE PRODUCT DATASHEET.

- G. DRAWING FILENAME: UC006ACrev4.

Figure 54. 6-Lead, 0.4 mm Pitch, WLCSP Package

## **Product-Specific Dimensions**

| Product      | D                     | E                         | Х           | Y            |

|--------------|-----------------------|---------------------------|-------------|--------------|

| FAN4860UC5X  | 1.230mm ±0.030 mm     | 0.880 mm ±0.030 mm        | 0.240 mm    | 0.215 mm     |

| FAN4860UC33X | 1.230Hill ±0.030 Hill | 0.000 11111 ±0.030 111111 | 0.240 11111 | 0.215 111111 |

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: http://www.fairchildsemi.com/dwg/UC/UC006AC.pdf.

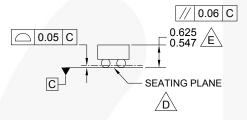

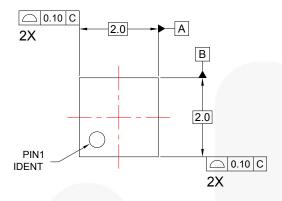

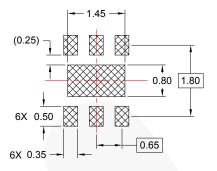

## **Physical Dimensions**

**TOP VIEW**

**BOTTOM VIEW**

#### RECOMMENDED LAND PATTERN

#### NOTES:

- (A) PACKAGE CONFORMS TO JEDEC MO-229 EXCEPT WHERE NOTED.

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994.

- D. LANDPATTERN RECOMMENDATION IS BASED ON FSC DESIGN ONLY.

- E. DRAWING FILENAME: MKT-UMLP06Erev2.

## Figure 55. 6-Lead, UMLP Package

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: http://www.fairchildsemi.com/dwg/UM/UMLP06E.pdf.

#### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

F-PFS™ AccuPower™ AX-CAP® FRFET<sup>®</sup> Global Power Resource SM BitSiC™ Build it Now™ GreenBridge™ Green FPS™ CorePLUS M Green FPS™ e-Series™ CorePOWER™ **CROSSVOLT** Gmax™ GTO™ Current Transfer Logic™ IntelliMAX™ DEUXPEED® ISOPLANAR™ Dual Cool™ Making Small Speakers Sound Louder

Dual Cool™ Making Small Speakers Sor EcoSPARK<sup>®</sup> and Better™ EfficientMax™ MegaBuck™

ESBC™ MICROCOUPLER™

MicroFET™ MicroPak™

Fairchild® MicroPak™ MicroPak2™

Fairchild Semiconductor® MillerDrive™

FACT Quiet Series™ MotionMax™

FACT®

FACT® MotionMax™

FACT® mWSaver®

FAST® OptoHiT™

FastvCore™ OPTOLOGIC®

FETBench™ OPTOLANAR®

PowerTrench<sup>®</sup> PowerXS™

Programmable Active Droop™

QS™ Quiet Series™ RapidConfigure™

Saving our world, 1mW/W/kW at a time™

SignalWise™

SmartMax™

SMART START™

Solutions for Your Success™

SPM®

STEALTH™

SuperFET®

SuperSOT™-3

SuperSOT™-6

SuperSOT™-8

SuperSOT™-8

SuperSOT™-8

SuprEMOS®

SyncFET™

SYSTEM

GENERAL®

TinyBoost®

TinyBuck®

TinyCalc™

TinyLogic®

TINYOPTO™

TinyPower™

TinyPWM™

TranSiC™

TriFault Detect™

TRUECURRENT®

LSEIDES™

Sync-Lock™

UHC®

Ultra FRFET®

UniFET®

VCX®

VisualMax®

VoltagePlus®

XS®

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

#### Definition of Terms

| Definition of Terms      |                       |                                                                                                                                                                                                     |

|--------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                          |

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |

| Preliminary              | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.                                                    |

Rev. 166

<sup>\*</sup> Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exp

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative