# ESDALC14-1BF4

Datasheet - production data

# Low clamping and low capacitance bidirectional single line ESD protection

## Features

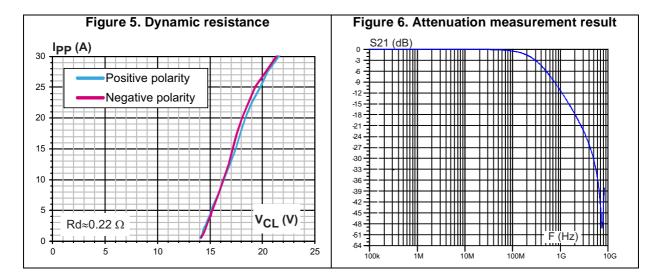

- Low clamping voltage: V<sub>CL</sub> = 18 V

- Bidirectional device

- Low leakage current

- 0201 package

- Ultra low PCB area: 0.18 mm<sup>2</sup>

- ECOPACK<sup>®</sup>2 compliant component

## Complies with the following standards

- IEC 61000-4-2:

- ±15 kV (air discharge)

- ±8 kV (contact discharge)

# Applications

Where transient over voltage protection in ESD sensitive equipment is required, such as:

- Smartphones, mobile phones and accessories

- Tablet, PC, netbooks and notebooks

- Portable multimedia devices and accessories

- Digital cameras and camcorders

- Communication and highly integrated systems

## Description

The ESDALC14-1BF4 is a bidirectional single line TVS diode designed to protect the data line or other I/O ports against ESD transients.

The device is ideal for applications where both reduced line capacitance and board space saving are required.

#### Figure 1. Functional diagram

DocID024898 Rev 2

This is information on a product in full production.

September 2015

# 1 Characteristics

| Symbol                         |                                                                                  | Value | Unit        |    |

|--------------------------------|----------------------------------------------------------------------------------|-------|-------------|----|

| V <sub>PP</sub> <sup>(1)</sup> | Peak pulse voltage IEC 61000-4-2 contact discharge   IEC 61000-4-2 air discharge |       | 25<br>30    | kV |

| P <sub>PP</sub> <sup>(1)</sup> | Peak pulse power (8/20 µs)                                                       |       | 100         | W  |

| I <sub>PP</sub> <sup>(1)</sup> | Peak pulse current (8/20 µs)                                                     |       | 5           | А  |

| Тj                             | Operating junction temperature range                                             |       | -40 to 150  | °C |

| T <sub>stg</sub>               | Storage temperature range                                                        |       | -65 to +150 | °C |

| ΤL                             | Maximum lead temperature fo                                                      | 260   | °C          |    |

| Table 1. | Absolute | maximum | ratings |

|----------|----------|---------|---------|

|----------|----------|---------|---------|

1. For a surge greater than the maximum values, the diode will fail in short-circuit.

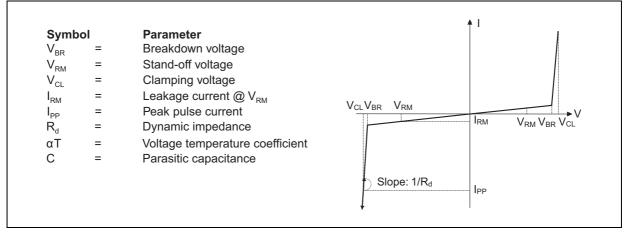

#### Figure 2. Electrical characteristics (definitions)

| Table 2. Electrical characteristics | (values, T <sub>amb</sub> = 25 °C) |

|-------------------------------------|------------------------------------|

|-------------------------------------|------------------------------------|

| Symbol            | Test conditions                                              | Value<br>Min. Typ. Max. |    |      | Unit |

|-------------------|--------------------------------------------------------------|-------------------------|----|------|------|

| Symbol            | Test conditions                                              |                         |    | Max. |      |

| V <sub>BR</sub>   | I <sub>R</sub> = 1 mA                                        | 13                      |    |      | V    |

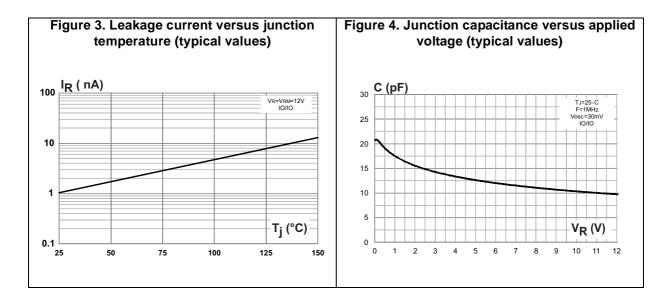

| I <sub>RM</sub>   | V <sub>RM</sub> = 12 V                                       |                         |    | 100  | nA   |

| VCL               | 8 kV contact discharge after 30 ns IEC 61000-4-2             |                         | 18 |      |      |

| C <sub>LINE</sub> | V <sub>LINE</sub> = 0 V, F = 1 MHz, V <sub>OSC</sub> = 30 mV | 22 25                   |    | pF   |      |

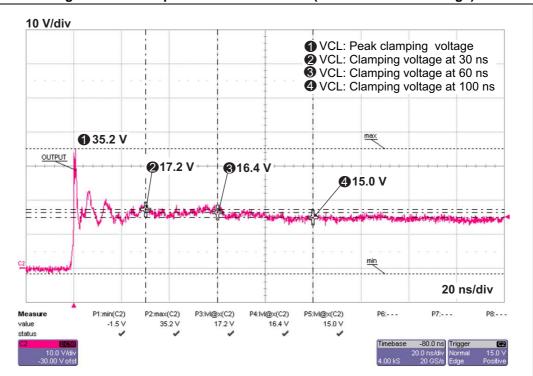

Figure 7. ESD response to IEC 61000-4-2 (+8 kV contact discharge)

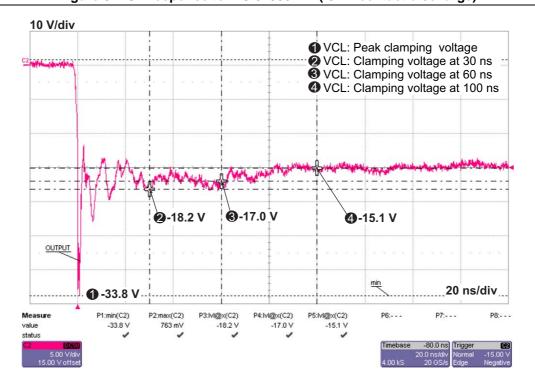

Figure 8. ESD response to IEC 61000-4-2 (-8 kV contact discharge)

DocID024898 Rev 2

# 2 Package information

- Epoxy meets UL94, V0

- Lead-free package

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com.* ECOPACK<sup>®</sup> is an ST trademark.

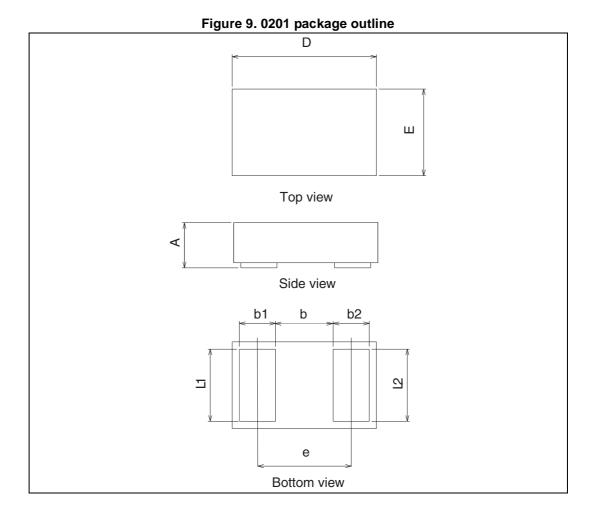

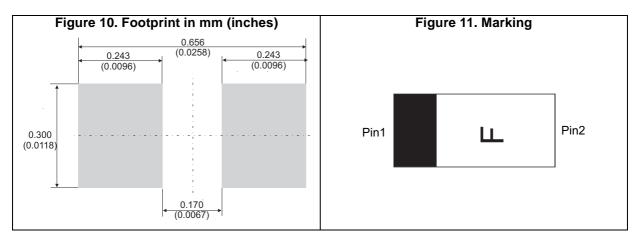

## 2.1 0201 package information

|      |            |             | i paonago ann |        |        |        |  |

|------|------------|-------------|---------------|--------|--------|--------|--|

|      | Dimensions |             |               |        |        |        |  |

| Ref. |            | Millimeters |               |        | Inches |        |  |

|      | Min.       | Тур.        | Max.          | Min.   | Тур.   | Max.   |  |

| А    | 0.28       | 0.30        | 0.32          | 0.0110 | 0.0118 | 0.0126 |  |

| b    | 0.19       | 0.21        | 0.23          | 0.0075 | 0.0082 | 0.0091 |  |

| b1   | 0.125      | 0.14        | 0.155         | 0.0049 | 0.0055 | 0.0061 |  |

| b2   | 0.125      | 0.14        | 0.155         | 0.0049 | 0.0055 | 0.0061 |  |

| D    | 0.57       | 0.60        | 0.63          | 0.0224 | 0.0236 | 0.0257 |  |

| е    | 0.33       | 0.35        | 0.37          | 0.0130 | 0.0138 | 0.0146 |  |

| Е    | 0.27       | 0.30        | 0.33          | 0.0106 | 0.0118 | 0.0130 |  |

| L1   | 0.175      | 0.19        | 0.205         | 0.0069 | 0.0075 | 0.0081 |  |

| L2   | 0.175      | 0.19        | 0.205         | 0.0069 | 0.0075 | 0.0081 |  |

# Note: The marking codes can be rotated by 90° or 180° to differentiate assembly location. In no case should this product marking be used to orient the component for its placement on a PCB. Only pin 1 mark is to be used for this purpose.

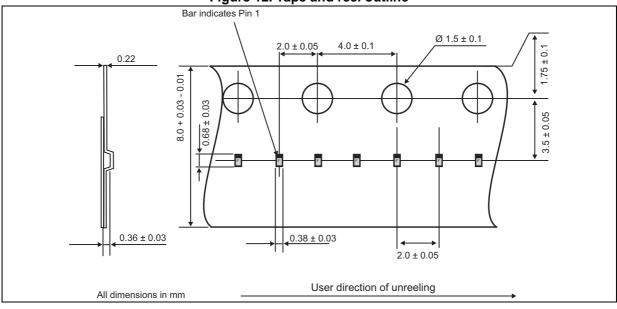

# 2.2 Packing information

# 3 Recommendation on PCB assembly

## 3.1 Stencil opening design

- 1. General recommendations on stencil opening design

- a) Stencil opening dimensions: L (Length), W (Width), T (Thickness).

#### Figure 13. Stencil opening dimensions

b) General design rule

Stencil thickness (T) = 75 ~ 125  $\mu$ m

Aspect Ratio =

$$\frac{W}{T} \ge 1.5$$

Aspect Area =

$$\frac{L \times W}{2T(L + W)} \ge 0.66$$

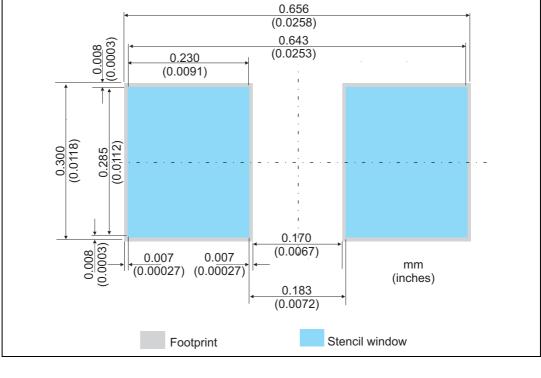

- 2. Recommended stencil window

- a) Stencil opening thickness: 80 µm

- b) Other dimensions: see Figure 14

#### Figure 14. Recommended stencil window position, stencil opening thickness: 80 $\mu m$

DocID024898 Rev 2

### 3.2 Solder paste

- 1. Use halide-free flux, qualification ROL0 according to ANSI/J-STD-004.

- 2. "No clean" solder paste recommended.

- 3. Offers a high tack force to resist component displacement during PCB movement.

- 4. Use solder paste with fine particles: Type 4 (powder particle size 20-48  $\mu m$  per IPC J STD-005).

### 3.3 Placement

- 1. Manual positioning is not recommended.

- 2. It is recommended to use the lead recognition capabilities of the placement system, not the outline centering.

- 3. Standard tolerance of ± 0.05 mm is recommended.

- 4. 1.0 N placement force is recommended. Too much placement force can lead to squeezed out solder paste and cause solder joints to short. Too low placement force can lead to insufficient contact between package and solder paste that could cause open solder joints or badly centered packages.

- 5. To improve the package placement accuracy, a bottom side optical control should be performed with a high resolution tool.

- 6. For assembly, a perfect supporting of the PCB (all the more on flexible PCB) is recommended during solder paste printing, pick and place and reflow soldering by using optimized tools.

## 3.4 PCB design preference

- 1. To control the solder paste amount, the closed via is recommended instead of open vias.

- 2. The position of tracks and open vias in the solder area should be well balanced. The symmetrical layout is recommended, in case any tilt phenomena caused by asymmetrical solder paste amount due to the solder flow away.

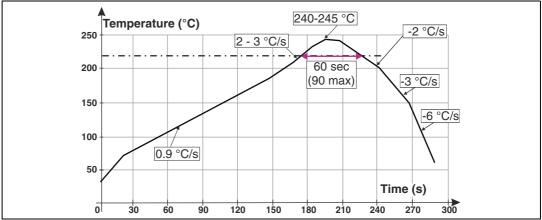

## 3.5 Reflow profile

Figure 15. ST ECOPACK<sup>®</sup> recommended soldering reflow profile for PCB mounting

Note: Minimize air convection currents in the reflow oven to avoid component movement.

# 4 Ordering information

|                    | ESDA LC 14 - 1 B F4 |

|--------------------|---------------------|

| ESD array          |                     |

| Low capacitance    |                     |

| Breakdown voltage  |                     |

| 14 = 13 V min      |                     |

| Number of lines    |                     |

| Directional        |                     |

| B = Bi-directional |                     |

| Package            |                     |

| F4 = 0201          |                     |

#### Figure 16. ordering information scheme

#### Table 4. Ordering information

| Order code    | Marking          | Package | Weight   | Base qty | Delivery mode |

|---------------|------------------|---------|----------|----------|---------------|

| ESDALC14-1BF4 | F <sup>(1)</sup> | 0201    | 0.116 mg | 15000    | Tape and reel |

1. The marking codes can be rotated by 90 °C or 180 °C to differentiate assembly location

# 5 Revision history

#### Table 5. Document revision history

| Date        | Revision | Changes          |  |

|-------------|----------|------------------|--|

| 11-Oct-2013 | 1        | First issue      |  |

| 03-Sep-2015 | 2        | Updated Table 2. |  |

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics - All rights reserved

DocID024898 Rev 2